Chapter 9 SDRAM Controller

9-20

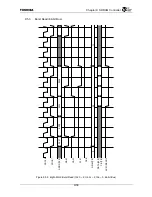

9.4.2

SDRAM Timing Register (SDCTR)

0x8040

63

48

Reserved

:Type

:Initial value

47 34

33

32

Reserved

DIA

R/W

:Type

1 1

:Initial

value

31 29 28 27 26 25 24 23 22 18 17 16

BC

ACP PT

RCD

ACE

PDAE

RC

CASL

DRB

R/W

R/W R/W

R/W

R/W

R/W R/W R/W

R/W

:Type

1 0 1 1 1 1 1 0 0 0 0 0 0 0 1 0

:Initial

value

15 14 13 12 11

0

DA

SWB

Reserved RP

R/W

R/W

R/W

:Type

1 1 0x30C

:Initial

value

Bit Mnemonic Field

Name

Description

Read/Write

63:34 —

— Reserved

⎯

33:32 DIA Write Active

Period

Data In to Active(t

DAL

) (Default: 11)

Specifies the period from the last Write data to the Active command.

00: Reserved

01: 4 t

CK

1

10: 5 t

CK

11: 6 t

CK

R/W

31:29

BC

Bank Cycle Time Bank Cycle Time (t

RC

) (Default: 101)

Specifies the bank cycle time.

2

000: 5 t

CK

100: 9 t

CK

001: 6 t

CK

101: 10 t

CK

010: 7 t

CK

110: Reserved

011: 8 t

CK

111: Reserved

R/W

28:27 ACP Active Command

Time

Active Command Period (t

RAS

) (Default: 11)

Specifies the active command time.

00: 3 t

CK

01: 4 t

CK

10: 5 t

CK

11: 6 t

CK

R/W

26

PT

Precharge Time

Precharge Time (t

RP

) (Default: 1)

Specifies the precharge time.

0: 2 t

CK

1: 3 t

CK

R/W

25

RCD

RAS-CAS Delay

RAS to CAS Delay (t

RCD

) (Default: 1)

Specifies the RAS - CAS delay.

0: 2 t

CK

1: 3 t

CK

R/W

Figure 9.4.2 SDRAM Timing Register (1/2)

1

t

CK

= Clock cycle

2

t

RC

is used during (i) refresh cycle time, (ii) single Read, (iii) two transfer burst Reads. The bank cycle time is t

RAS

+

t

RP

+ 1t

CK

if t

RAS

+ t

RP

< t

RC

in the case of (ii) (iii).

Содержание TX49 TMPR4937

Страница 1: ...64 Bit TX System RISC TX49 Family TMPR4937 Rev 2 0 ...

Страница 4: ......

Страница 13: ...Table of Contents ix TMPR4937 Revision History 1 ...

Страница 14: ...Table of Contents x ...

Страница 15: ...Handling Precautions ...

Страница 16: ......

Страница 18: ...1 Using Toshiba Semiconductors Safely 1 2 ...

Страница 40: ...3 General Safety Precautions and Usage Considerations 3 18 ...

Страница 42: ...4 Precautions and Usage Considerations 4 2 ...

Страница 43: ...TMPR4937 2005 3 Rev 2 0 ...

Страница 44: ......

Страница 52: ...Chapter 1 Overview and Features 1 6 ...

Страница 156: ...Chapter 7 External Bus Controller 7 56 ...

Страница 491: ...Chapter 16 Removed 16 1 16 Removed ...

Страница 492: ...Chapter 16 Removed 16 2 ...

Страница 493: ...Chapter 17 Removed 17 1 17 Removed ...

Страница 494: ...Chapter 17 Removed 17 2 ...

Страница 495: ...Chapter 18 Removed 18 1 18 Removed ...

Страница 496: ...Chapter 18 Removed 18 2 ...

Страница 497: ...Chapter 19 Removed 19 1 19 Removed ...

Страница 498: ...Chapter 19 Removed 19 2 ...

Страница 506: ...Chapter 20 Extended EJTAG Interface 20 8 ...

Страница 529: ...Chapter 22 Pinout and Package Information 22 9 22 2 Package Dimensions P BGA484 3535 1 27B9 Unit mm ...

Страница 530: ...Chapter 22 Pinout and Package Information 22 10 ...

Страница 542: ...Chapter 24 Parts Number when Ordering 24 2 ...

Страница 544: ...Appendix A TX49 H3 Core Supplement A 2 ...