NOVA electronics Inc. MCX514 -

175

-

175

-

D9 TIMER

Interrupt occurs when the timer expires.

D10 SPLTP

Interrupt occurs at the

↑

of a pulse in each split pulse. (When the split pulse logic is set to Hi pulse)

D11 SPLTE

Interrupt occurs when the split pulse is finished.

D15

~

12 SYNC3

~

0

Interrupt occurs when synchronous action SYNC3~0 is activated.

D15~D0 will be set to 0 at reset.

6.6

Mode Register2: WR2

Each axis has mode register WR2 individually. The host CPU specifies the mode register of which axis should be accessed

depends on the axis of written command just before. Or the user can specify the axis by writing NOP command with axis

assignment.

Mode register WR2 is used for setting: (1). input signal nSTOP2~ nSTOP0 (decelerating stop / instant stop during the driving),

(2). input signal for a servo motor, (3). external limit inputs, (4). software limit.

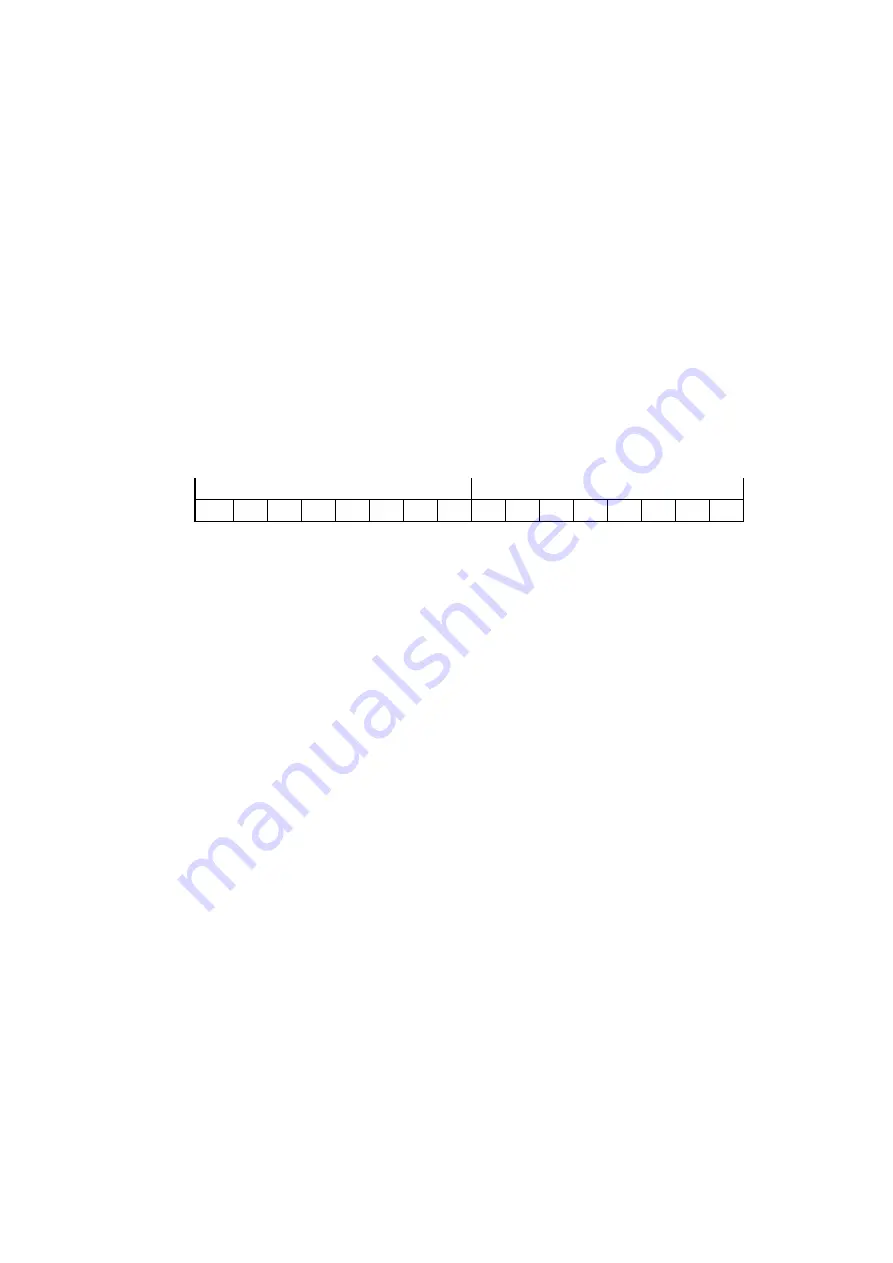

D7

D6

D5

D4

H

L

D15

D14

D13

D12

D11

D10

D9

D8

D3

D2

D1

D0

WR2

SP2-E

INP-E

SP1-E

SP0-E

SP2-L

INP-L

SP1-L

SP0-L

ALM-E ALM-L

HLM-L

HLM-E

HLM-M

SLM-E

SLM-O

SLM-M

D4,2,0 SPk-L

The bit for setting enable logical levels for driving stop input signal nSTOPk (k:2

~

0).

0: active on the Low level, 1: active on the Hi level

In automatic home search, the logical level of the nSTOPk signal that is used is set in these bits.

D5,3,1 SPk-E

The bit for setting enable / disable of driving stop input signal nSTOPk (k:2

~

0).

0: disable, 1: enable

Once nSTOP2~ nSTOP0 are active and then driving starts, when nSTOPk signal becomes active level, the

decelerating stop will be performed during acceleration / deceleration driving and the instant stop will be

performed during constant speed driving.

In automatic home search, the enable / disable bits of nSTOPk that are used should be set to disable.

D6 INP-L

Setting logical level of in-position input signal nINPOS from a servo driver.

0: active on the Low level, 1: active on the Hi level

D7 INP-E

Setting enable / disable of nINPOS input signal.

0: disable, 1: enable

When it is enabled, the DRIVE bit of RR0 (main status) register does not return to 0 until nINPOS signal is

on its active level after the driving is finished.

D8 ALM-L

Setting active level of servo alarm input signal nALARM.

0: active on the Low level, 1: active on the Hi level

D9 ALM-E

Setting enable / disable of input signal nALARM.

0: disable, 1: enable

When it is enabled, it checks input signal nALARM during the driving. And if it is active, D4 (ALARM) bit

of RR2 register will become 1 and the driving will stop.

D10 HLM-L

Setting logical level of hardware limit input signals nLMTP, nLMTM.

0: active on the Low level, 1: active on the Hi level

D11 HLM-E

Setting enable / disable of nLMTP, nLMTM limit input signals.

0: disable, 1: enable

Once it is enabled, if nLMTP limit input signal is active during the + direction driving, D2 (HLMT+) bit of

RR2 register will become 1 and if nLMTM

limit input signal is active during the − direction driving, D3