36

Document # 001-20559 Rev. *D

CPU Core (M8C)

2.4

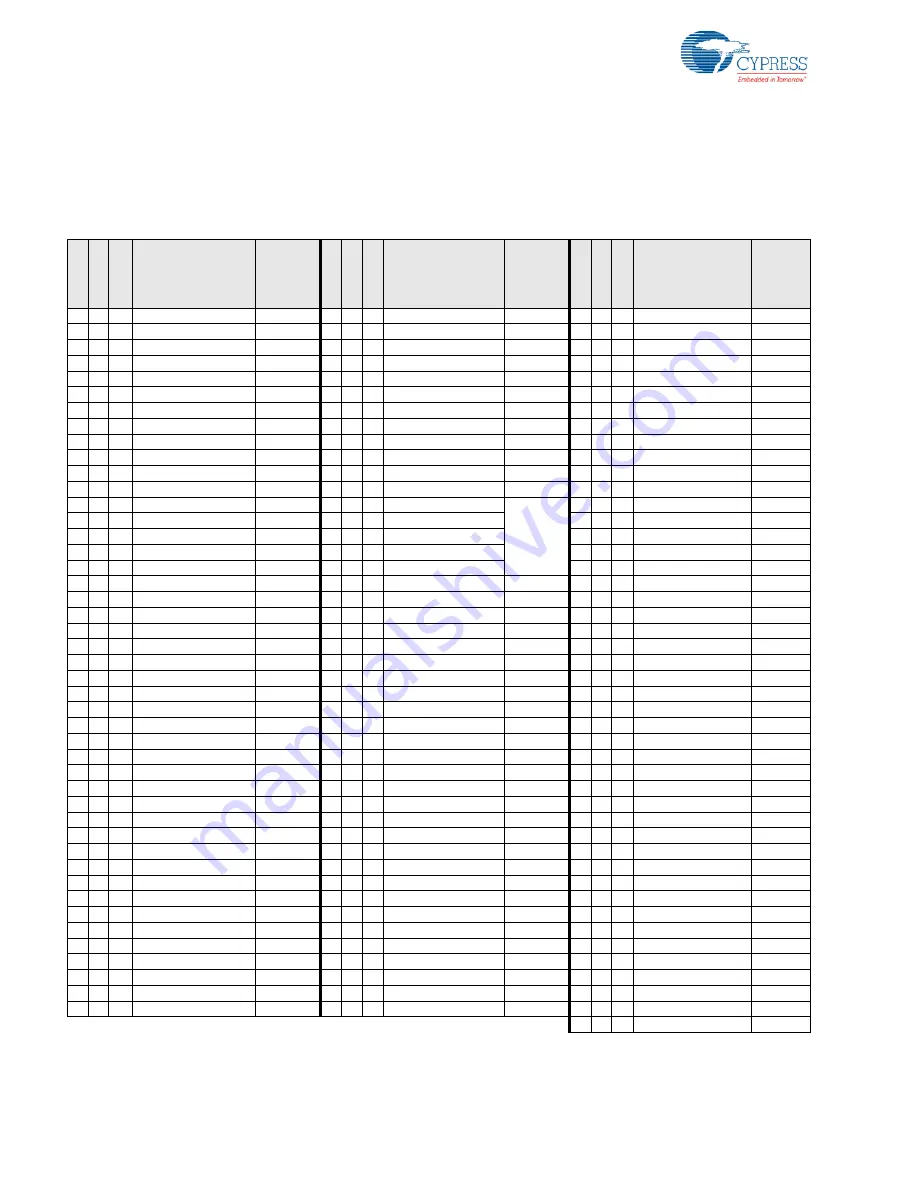

Instruction Set Summary

The instruction set is summarized in both

and

(in numeric and

order, respectively), and serves

as a quick reference. If more information is needed, the Instruction Set Summary tables are described in detail in the

PSoC

Designer Assembly Language User Guide

(refer to

http://www.cypress.com/psoc

).

Table 2-1. Instruction Set Summary Sorted Numerically by Opcode

Op

c

o

d

e

Hex

Cycl

es

Bytes

Instruction Format

Flags

Op

c

o

d

e

Hex

Cycl

es

Bytes

Instruction Format

Flags

Op

c

o

d

e

Hex

Cycl

es

Bytes

Instruction Format

Flags

00 15

1 SSC

2D

8

2 OR [X+expr], A

Z

5A

5

2 MOV [expr], X

01

4

2 ADD A, expr

C, Z

2E

9

3 OR [expr], expr

Z

5B

4

1 MOV A, X

Z

02

6

2 ADD A, [expr]

C, Z

2F 10

3 OR [X+expr], expr

Z

5C

4

1 MOV X, A

03

7

2 ADD A, [X+expr]

C, Z

30

9

1 HALT

5D

6

2 MOV A, reg[expr]

Z

04

7

2 ADD [expr], A

C, Z

31

4

2 XOR A, expr

Z

5E

7

2 MOV A, reg[X+expr]

Z

05

8

2 ADD [X+expr], A

C, Z

32

6

2 XOR A, [expr]

Z

5F 10

3 MOV [expr], [expr]

06

9

3 ADD [expr], expr

C, Z

33

7

2 XOR A, [X+expr]

Z

60

5

2 MOV reg[expr], A

07 10

3 ADD [X+expr], expr

C, Z

34

7

2 XOR [expr], A

Z

61

6

2 MOV reg[X+expr], A

08

4

1 PUSH A

35

8

2 XOR [X+expr], A

Z

62

8

3 MOV reg[expr], expr

09

4

2 ADC A, expr

C, Z

36

9

3 XOR [expr], expr

Z

63

9

3 MOV reg[X+expr], expr

0A

6

2 ADC A, [expr]

C, Z

37 10

3 XOR [X+expr], expr

Z

64

4

1 ASL A

C, Z

0B

7

2 ADC A, [X+expr]

C, Z

38

5

2 ADD SP, expr

65

7

2 ASL [expr]

C, Z

0C

7

2 ADC [expr], A

C, Z

39

5

2 CMP A, expr

if (A=B) Z=1

if (A<B) C=1

66

8

2 ASL [X+expr]

C, Z

0D

8

2 ADC [X+expr], A

C, Z

3A

7

2 CMP A, [expr]

67

4

1 ASR A

C, Z

0E

9

3 ADC [expr], expr

C, Z

3B

8

2 CMP A, [X+expr]

68

7

2 ASR [expr]

C, Z

0F 10

3 ADC [X+expr], expr

C, Z

3C

8

3 CMP [expr], expr

69

8

2 ASR [X+expr]

C, Z

10

4

1 PUSH X

3D

9

3 CMP [X+expr], expr

6A

4

1 RLC A

C, Z

11

4

2 SUB A, expr

C, Z

3E 10

2 MVI A, [ [expr]++ ]

Z

6B

7

2 RLC [expr]

C, Z

12

6

2 SUB A, [expr]

C, Z

3F 10

2 MVI [ [expr]++ ], A

6C

8

2 RLC [X+expr]

C, Z

13

7

2 SUB A, [X+expr]

C, Z

40

4

1 NOP

6D

4

1 RRC A

C, Z

14

7

2 SUB [expr], A

C, Z

41

9

3 AND reg[expr], expr

Z

6E

7

2 RRC [expr]

C, Z

15

8

2 SUB [X+expr], A

C, Z

42 10

3 AND reg[X+expr], expr

Z

6F

8

2 RRC [X+expr]

C, Z

16

9

3 SUB [expr], expr

C, Z

43

9

3 OR reg[expr], expr

Z

70

4

2 AND F, expr

C, Z

17 10

3 SUB [X+expr], expr

C, Z

44 10

3 OR reg[X+expr], expr

Z

71

4

2 OR F, expr

C, Z

18

5

1 POP A

Z

45

9

3 XOR reg[expr], expr

Z

72

4

2 XOR F, expr

C, Z

19

4

2 SBB A, expr

C, Z

46 10

3 XOR reg[X+expr], expr

Z

73

4

1 CPL A

Z

1A

6

2 SBB A, [expr]

C, Z

47

8

3 TST [expr], expr

Z

74

4

1 INC A

C, Z

1B

7

2 SBB A, [X+expr]

C, Z

48

9

3 TST [X+expr], expr

Z

75

4

1 INC X

C, Z

1C

7

2 SBB [expr], A

C, Z

49

9

3 TST reg[expr], expr

Z

76

7

2 INC [expr]

C, Z

1D

8

2 SBB [X+expr], A

C, Z

4A 10

3 TST reg[X+expr], expr

Z

77

8

2 INC [X+expr]

C, Z

1E

9

3 SBB [expr], expr

C, Z

4B

5

1 SWAP A, X

Z

78

4

1 DEC A

C, Z

1F 10

3 SBB [X+expr], expr

C, Z

4C

7

2 SWAP A, [expr]

Z

79

4

1 DEC X

C, Z

20

5

1 POP X

4D

7

2 SWAP X, [expr]

7A

7

2 DEC [expr]

C, Z

21

4

2 AND A, expr

Z

4E

5

1 SWAP A, SP

Z

7B

8

2 DEC [X+expr]

C, Z

22

6

2 AND A, [expr]

Z

4F

4

1 MOV X, SP

7C 13

3 LCALL

23

7

2 AND A, [X+expr]

Z

50

4

2 MOV A, expr

Z

7D

7

3 LJMP

24

7

2 AND [expr], A

Z

51

5

2 MOV A, [expr]

Z

7E 10

1 RETI

C, Z

25

8

2 AND [X+expr], A

Z

52

6

2 MOV A, [X+expr]

Z

7F

8

1 RET

26

9

3 AND [expr], expr

Z

53

5

2 MOV [expr], A

8x

5

2 JMP

27 10

3 AND [X+expr], expr

Z

54

6

2 MOV [X+expr], A

9x

11

2 CALL

28 11

1 ROMX

Z

55

8

3 MOV [expr], expr

Ax

5

2 JZ

29

4

2 OR A, expr

Z

56

9

3 MOV [X+expr], expr

Bx

5

2 JNZ

2A

6

2 OR A, [expr]

Z

57

4

2 MOV X, expr

Cx

5

2 JC

2B

7

2 OR A, [X+expr]

Z

58

6

2 MOV X, [expr]

Dx

5

2 JNC

2C

7

2 OR [expr], A

Z

59

7

2 MOV X, [X+expr]

Ex

7

2 JACC

Note 1

Interrupt acknowledge to Interrupt Vector table = 13 cycles.

Fx 13

2 INDEX

Z

Note 2

The number of cycles required by an instruction is increased by one for instructions that span

256 byte page boundaries in the Flash memory space.

Summary of Contents for PSoC CY8C23533

Page 4: ...Contents Overview 4 Document 001 20559 Rev D Section G Glossary 385 Index 401 ...

Page 16: ...Contents Overview 16 Document 001 20559 Rev D ...

Page 24: ...24 Document 001 20559 Rev D Section A Overview ...

Page 30: ...30 Document 001 20559 Rev D Pin Information ...

Page 54: ...54 Document 001 20559 Rev D Supervisory ROM SROM ...

Page 60: ...60 Document 001 20559 Rev D RAM Paging ...

Page 68: ...68 Document 001 20559 Rev D Interrupt Controller ...

Page 76: ...12 Document 001 20559 Rev D General Purpose IO GPIO ...

Page 82: ...18 Document 001 20559 Rev D Internal Main Oscillator IMO ...

Page 84: ...20 Document 001 20559 Rev D Internal Low Speed Oscillator ILO ...

Page 90: ...26 Document 001 20559 Rev D External Crystal Oscillator ECO ...

Page 94: ...30 Document 001 20559 Rev D Phase Locked Loop PLL ...

Page 106: ...42 Document 001 20559 Rev D Sleep and Watchdog ...

Page 228: ...164 Document 001 20559 Rev D Section D Digital System ...

Page 234: ...170 Document 001 20559 Rev D Array Digital Interconnect ADI ...

Page 278: ...214 Document 001 20559 Rev D Digital Blocks ...

Page 296: ...232 Document 001 20559 Rev D Analog Interface ...

Page 304: ...240 Document 001 20559 Rev D Analog Array ...

Page 308: ...244 Document 001 20559 Rev D Analog Input Configuration ...

Page 312: ...248 Document 001 20559 Rev D Analog Reference ...

Page 338: ...274 Document 001 20559 Rev D Section F System Resources ...

Page 354: ...290 Document 001 20559 Rev D Multiply Accumulate MAC ...

Page 374: ...310 Document 001 20559 Rev D I2C ...

Page 400: ...336 Document 001 20559 Rev D Section G Glossary ...