Copyright © Siemens AG 2016. All rights reserved

348

ERTEC 200P-2 Manual

Technical data subject to change

Version 1.0

3

RFF

0h r

Receive FIFO full

4

BSY

0h r

SSP busy flag

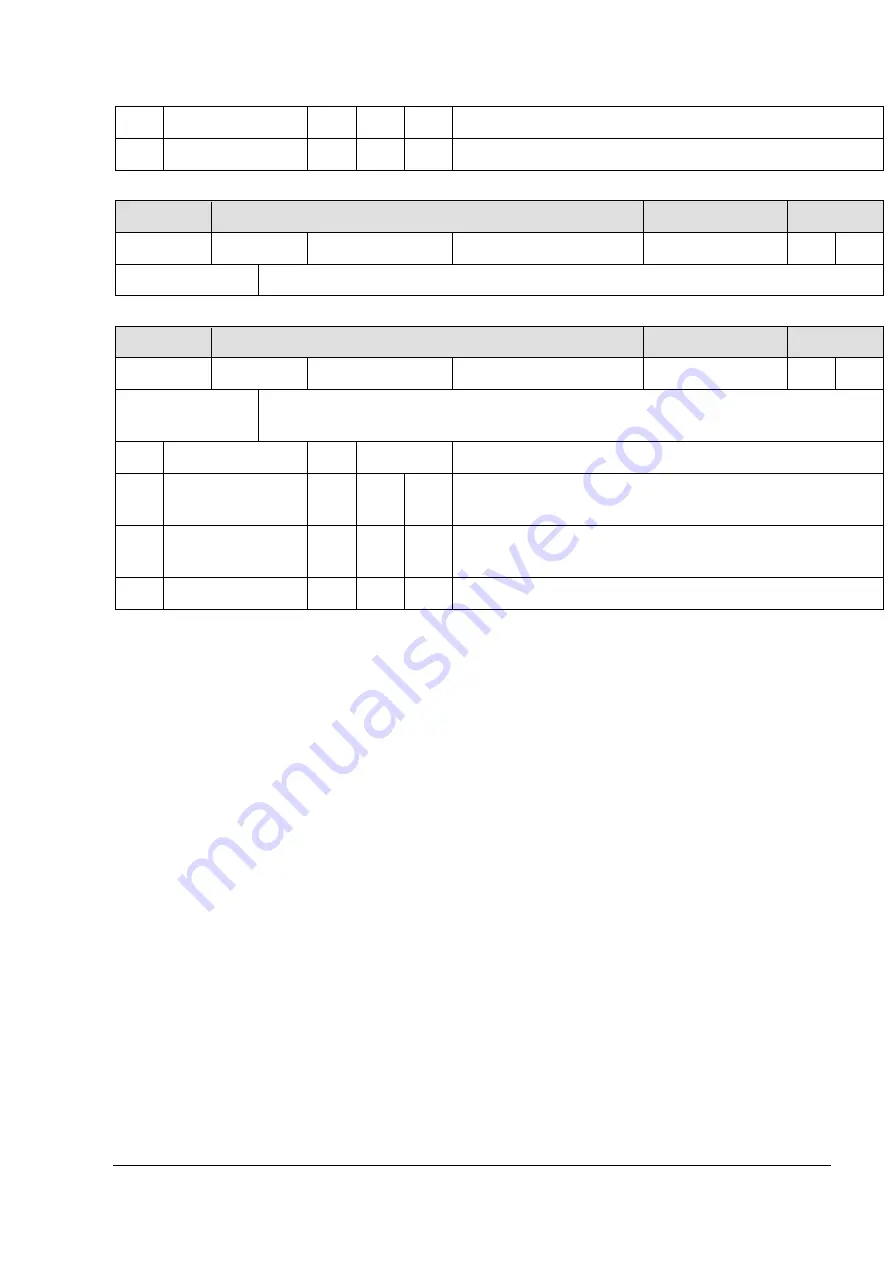

Register:

SSPCPSR

Address:

10h

Bits:

7dt0

Reset value:

00h

Attributes:

r

w

Description:

Clock prescale divisor

Register:

SSPIIR_SSPICR

Address:

14h

Bits:

2dt0

Reset value:

0h

Attributes:

rh

Description:

The interrupt status is read from the SSP interrupt identification register

(SSPIIR)

Bit Identifier

Reset Attr.

Function / Description

0

RIS

0h rh

Read: SSP transmit FIFO service request interrupt

status

1

TIS

0h rh

Read: SSP Receive FIFO service request interrupt

status

2

RORIS

0h rh

Read: SSP Receive FIFO overrun interrupt status

2.3.10.8

GPIO (General Purpose Input / Output)

There are a maximum of 96 general purpose input/outputs (GPIOs). They are divided into

2 blocks:

GPIO31-0: 32-bit (available as default GPIO port)

GPIO95-32: 64-bit (available as an alternative to XHIF)

GPIO31-0

is available as a default block and is multiplexed with the interface signals from

the PNPLL, UART2/3, SPI1/2, I

2

C_1_3, timer 0 – 5 and ARM926 watchdog . Following a

reset, this GPIO block is selected and connected to all inputs. The alternate functions are

set by the SW using the GPIO registers (see 2.3.10.8.5).

The internal MII debug interface (internal PHYs) is also multiplexed to GPIO31-0. This

function is set upon an XRESET PowerOn reset with the configuration pins CONFIG(6-3)

(see 2.3.10.9.3) or by the SW in the SCRB register 'Config-REG(6-3)' (see 2.3.10.9.22).

Rules for the SW: The default values of the alternate functions must not be changed if

the internal MII debug interfaces are selected at the corresponding pins with the configu-

ration pins.

The GPIO15-0 inputs are also connected to an I-filter (see 2.3.10.1) and to the ARM

interrupt controller (IRQ32-47, see 2.3.2.14). The polarity of these signals to the ARM

interrupt controller can be set in the GPIO_INT_POLSEL register (see 2.3.10.9.22). In

line with the polarity of the external signals, this ensures a high-active interrupt level.

Содержание ERTEC 200P

Страница 1: ...ERTEC 200P 2 Enhanced Real Time Ethernet Controller Manual ...

Страница 309: ...Copyright Siemens AG 2016 All rights reserved 309 ERTEC 200P 2 Manual Technical data subject to change Version 1 0 ...

Страница 492: ...Copyright Siemens AG 2016 All rights reserved 492 ERTEC 200P 2 Manual Technical data subject to change Version 1 0 ...