Copyright © Siemens AG 2016. All rights reserved

78

ERTEC 200P-2 Manual

Technical data subject to change

Version 1.0

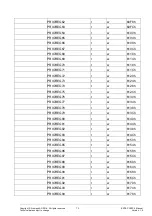

Register:

MASKREG0

Address:

5000h

Bits:

31dt0

Reset value:

FFFFFFFFh

Attributes:

r

w

Description:

Interrupt Mask Register

Enable/disable the interrupt inputs

0 – 31 inputs of the interrupt controller

0' = Interrupt input enabled

'1' = Interrupt input disabled

Register:

MASKREG1

Address:

5004h

Bits:

31dt0

Reset value:

FFFFFFFFh

Attributes:

r

w

Description:

Interrupt Mask Register

Enable/disable the interrupt inputs

32 – 63 inputs of the interrupt controller

0' = Interrupt input enabled

'1' = Interrupt input disabled

Register:

MASKREG2

Address:

5008h

Bits:

31dt0

Reset value:

FFFFFFFFh

Attributes:

r

w

Description:

Interrupt Mask Register

Enable/disable the interrupt inputs

64 – 95 inputs of the interrupt controller

0' = Interrupt input enabled

'1' = Interrupt input disabled

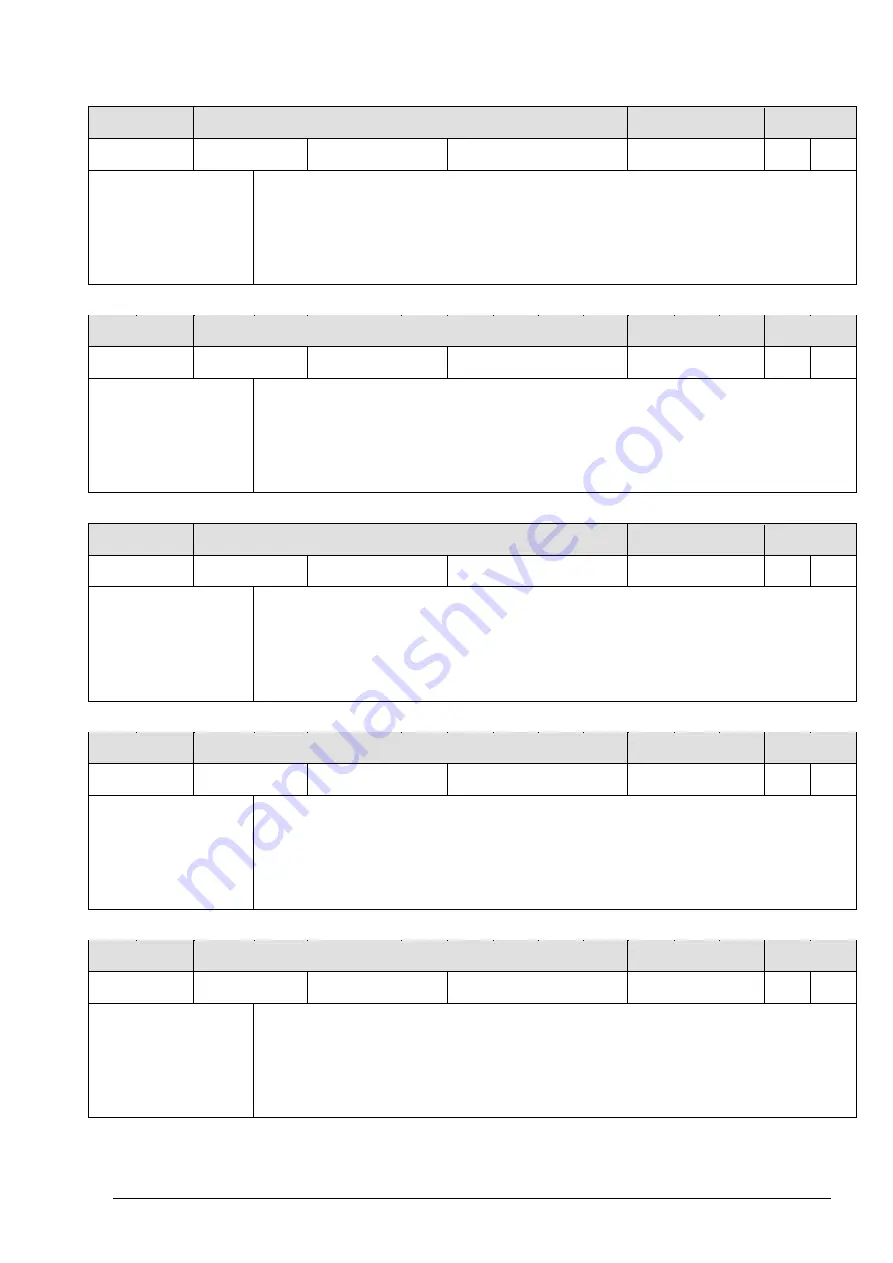

Register:

IRR0

Address:

5100h

Bits:

31dt0

Reset value:

00000000h

Attributes:

rh

Description:

Request Register

Flag for the Interrupt Request detected as result of a positive edge

0 – 31 inputs of the interrupt controller

'0' = No request

'1' = Request has occurred

Register:

IRR1

Address:

5104h

Bits:

31dt0

Reset value:

00000000h

Attributes:

rh

Description:

Request Register

Flag for the Interrupt Request detected as result of a positive edge

32 – 63 inputs of the interrupt controller

'0' = No request

'1' = Request has occurred

Содержание ERTEC 200P

Страница 1: ...ERTEC 200P 2 Enhanced Real Time Ethernet Controller Manual ...

Страница 309: ...Copyright Siemens AG 2016 All rights reserved 309 ERTEC 200P 2 Manual Technical data subject to change Version 1 0 ...

Страница 492: ...Copyright Siemens AG 2016 All rights reserved 492 ERTEC 200P 2 Manual Technical data subject to change Version 1 0 ...