Intel

®

IXP45X and Intel

®

IXP46X Product Line of Network Processors

August 2006

Developer’s Manual

Order Number: 306262-004US

899

I2C Bus Interface Unit—Intel

®

IXP45X and Intel

®

IXP46X Product Line of Network Processors

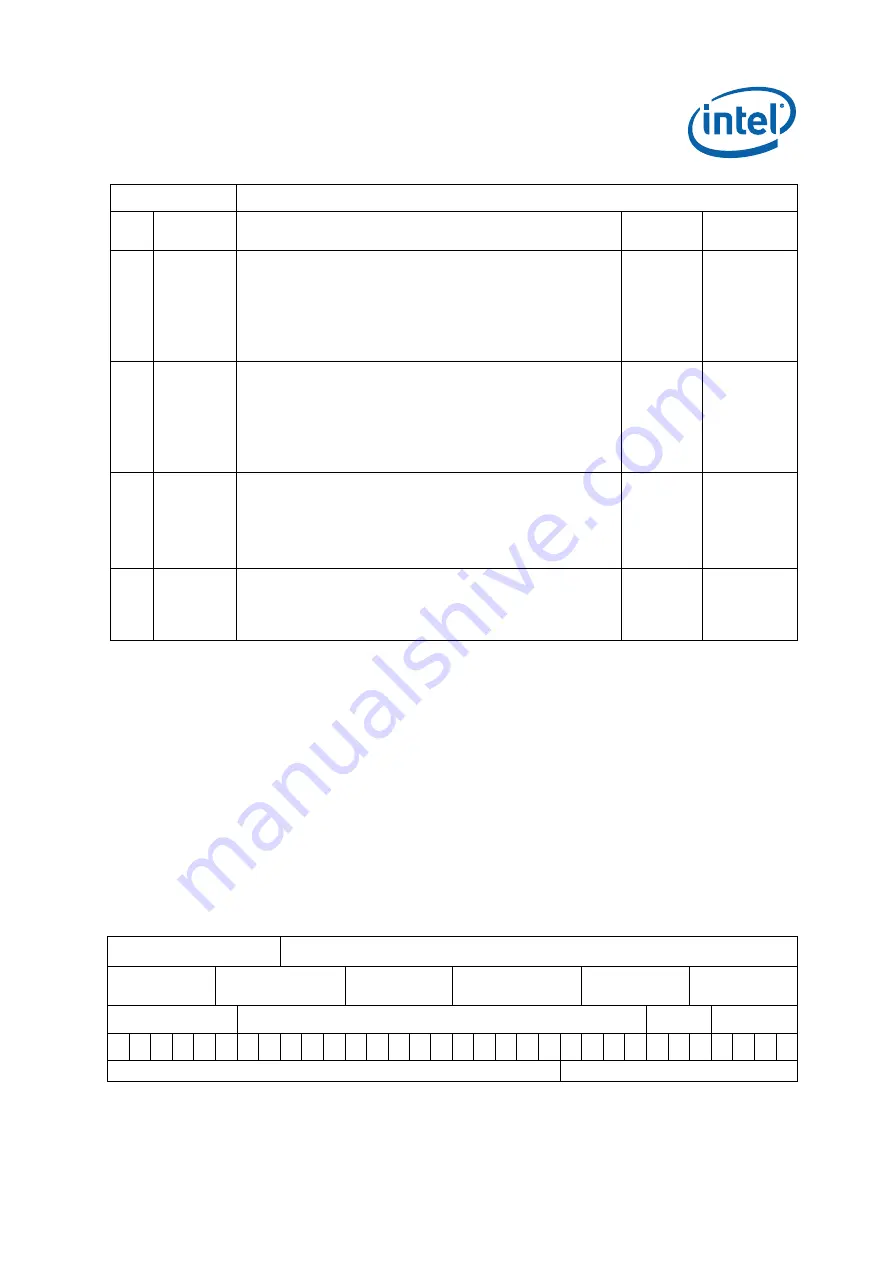

21.10.2

I

2

C Status Register - ISR

I

2

C

interrupts are signalled to the interrupt controller of the IXP45X/IXP46X network

processors by the I

2

C

Interrupt Status Register (ISR). Software uses the ISR bits to

check the status of the I

2

C unit and bus. ISR bits (bits 9-5) are updated after the Ack/

Nack bit has completed on the I

2

C bus.

The ISR is also used to clear interrupts signalled from the I

2

C Bus Interface Unit. These

are:

• IDBR Receive Full

• IDBR Transmit Empty

• Slave Address Detected

• Bus Error Detected

• STOP Condition Detect

• Arbitration Lost

03

Transfer Byte

Transfer Byte: used to send/receive a byte on the I

2

C bus.

0 = Cleared by I

2

C unit when the byte is sent/received.

1 = Send/receive a byte.

The IXP45X/IXP46X network processors

c

an monitor this bit to

determine when the byte transfer has completed. In master or slave

mode, after each byte transfer including Ack/Nack bit, the I

2

C unit

holds the SCL line low (inserting wait states) until the Transfer Byte bit

is set.

0

RW

02

Ack/Nack

Control

Ack/Nack Control: defines the type of Ack pulse sent by the I

2

C unit

when in master receive mode.

0 = The I

2

C unit sends an Ack pulse after receiving a data byte.

1 = The I

2

C unit sends a negative Ack (Nack) after receiving a data

byte.

The I

2

C unit automatically sends an Ack pulse when responding to its

slave address or when responding in slave-receive mode, independent

of the Ack/Nack control bit setting.

0

RW

01

STOP

STOP: used to initiate a STOP condition after transferring the next

data byte on the I

2

C bus when in master mode. In master-receive

mode, the Ack/Nack control bit must be set in conjunction with this

bit. See

Section 21.4.3.3, “STOP Condition” on page 881

for more

details on the STOP state.

0 = Do not send a STOP.

1 = Send a STOP.

0

RW

00

START

START: used to initiate a START condition to the I

2

C unit when in

Section 21.4.3.1, “START Condition” on page 880

for more details on the START state.

0 = Do not send a START.

1 = Send a START.

0

RW

Register

I

2

C Control Register (Sheet 3 of 3)

Bits

Name

Description

Reset

Value

Access

Register Name:

I

2

C Status Register - ISR

Block

Base Address:

0xC801_1004

Offset Address

Reg

OffsetAddress

Reset Value

0x0000_0000

Register Description:

I

2

C Status Register - ISR

Access:

(See below.)

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

(Reserved)

See table below.