Intel

®

IXP45X and Intel

®

IXP46X Product Line of Network Processors

August 2006

Developer’s Manual

Order Number: 306262--, Revision: 004US

383

USB 2.0 Host Controller—Intel

®

IXP45X and Intel

®

IXP46X Product Line of Network Processors

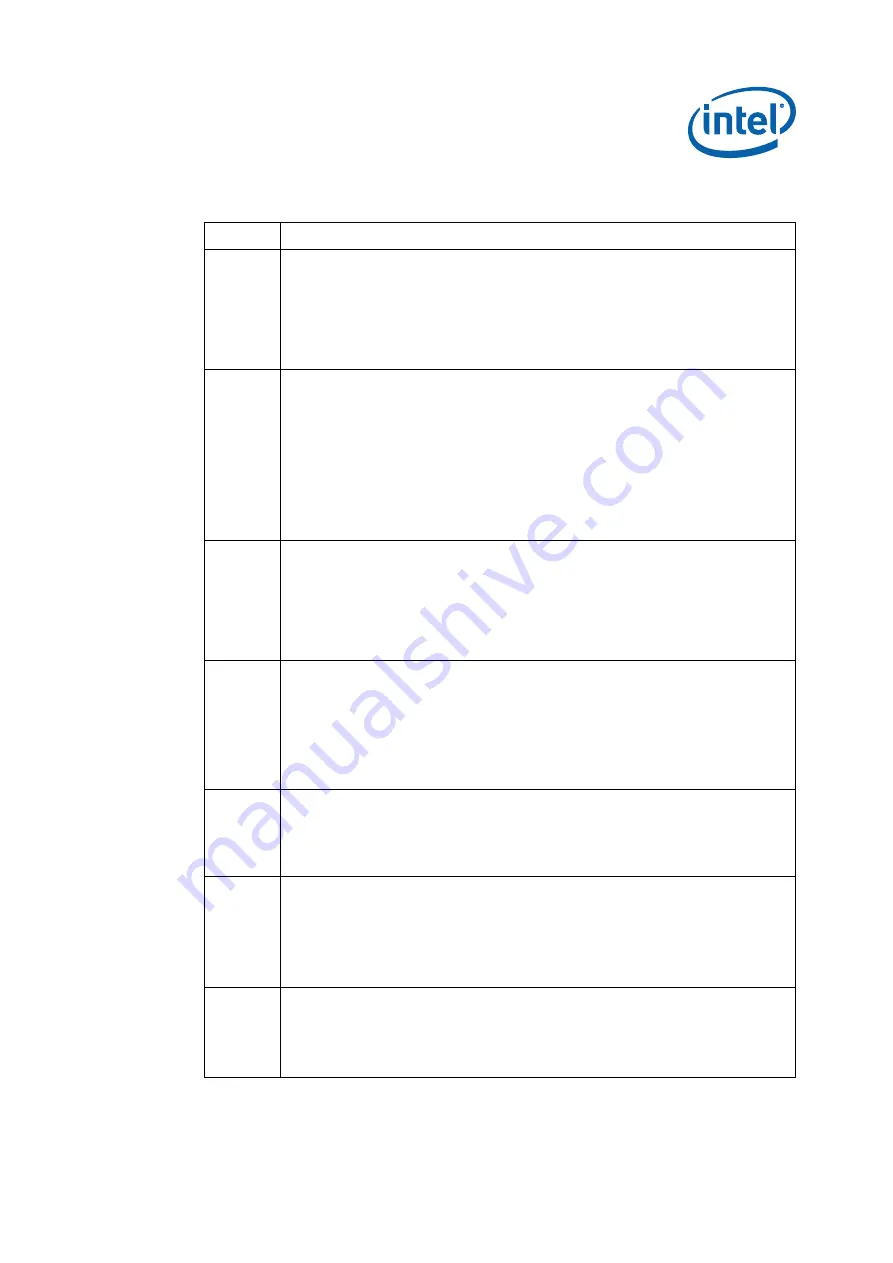

Table 141.

PORTSCx - Port Status Control[1:8] (Sheet 1 of 4)

Field

Description

PTS

Parallel Transceiver Select – Read/Write. This register bit is used in conjunction with the

configuration constant VUSB_HS_PHY_MODE to control which parallel transceiver interface is

selected. If VUSB_HS_PHY_MODE is set for 0,1 or 2 then this bit is read only. If

VUSB_HS_PHY_MODE is 3,4 or 5 then this bit is read/write. This bit is reset to 1 if

VUSB_HS_PHY_MODE selects a default interface of Philips*, else it is reset to 0.

Writing this bit to 0 selects the UTMI parallel Interface.

Writing to 1 selects the Philips parallel Interface.

This bit is not defined in the EHCI specification.

STS

Serial Transceiver Select – Read/Write. This register bit is used in conjunction with the

configuration constant VUSB_HS_PHY_MODE to control whether the parallel or serial

transceiver interface is selected. If VUSB_HS_PHY_MODE is set for 0,1 or 2 then this bit is read

only. If VUSB_HS_PHY_MODE is 3,4 or 5 then this bit is read/write. This bit is reset to 1 if

VUSB_HS_PHY_MODE selects a default interface of Serial FS else it is reset to 0.

Writing this bit to 0 selects the parallel transceiver Interface.

Writing this bit to 1 selects the Serial (Full Speed) transceiver interface.

For the UTMI interface, this bit can be used to select between a Parallel UTMI PHY and a

standard 1.1 PHY. For the Philips interface, this bit is used to prevent use of the Parallel PHY and

generate signalling exclusively through the serial interface. (For Philips this also implies no

chirping.)

This bit is not defined in the EHCI specification.

PTW

Parallel Transceiver Width – Read/Write. This register bit is used in conjunction with the

configuration constant VUSB_HS_PHY8_16 to control whether the data bus width of the UTMI

transceiver interface. If VUSB_HS_PHY8_16 is set for 0 or 1 then this bit is read only. If

VUSB_HS_PHY8_16 is 2 or 3 then this bit is read/write. This bit is reset to 1 if

VUSB_HS_PHY8_16 selects a default UTMI interface width of 16-bits else it is reset to 0.

Writing this bit to 0 selects the 8-bit [60MHz] UTMI interface.

Writing this bit to 1 selects the 16-bit [30MHz] UTMI interface.

This bit is not defined in the EHCI specification.

PSPD

Port Speed – Read Only. This register field indicates the speed at which the port is operating.

For HS mode operation in the host controller the port routing steers data to the Protocol engine.

For FS and LS mode operation in the host controller, the port routing steers data to the Protocol

Engine w/ Embedded Transaction Translator. This implementation does not support HS mode of

operation.

00 – Full Speed

01 – Low Speed

10 – High Speed (Not supported)

This bit is not defined in the EHCI specification.

PFSC

Port Force Full Speed Connect – Read/Write. Default = 0b. Writing this bit to a 1b will

force the port to only connect at Full Speed. It disables the chirp sequence that allows the port

to identify itself as High Speed. This is useful for testing FS configurations with a HS host, hub

or device.

This bit is not defined in the EHCI specification.

This bit is for debugging purposes.

PHCD

PHY Low Power Suspend - Clock Disable (PLPSCD) – Read/Write. Default = 0b. Writing

this bit to a 1b will disable the PHY clock. Writing a 0b enables it. Reading this bit will indicate

the status of the PHY clock. NOTE: The PHY clock cannot be disabled if it is being used as the

system clock.

In host mode, the PHY can be put into Low Power Suspend – Clock Disable when the

downstream device has been put into suspend mode or when no downstream device is

connected. Low power suspend is completely under the control of software.

This bit is not defined in the EHCI specification.

WKOC

Wake on Over-current Enable (WKOC_E) — Read/Write.

Default = 0b. Writing this bit to a one enables the port to be sensitive to over-current

conditions as wake-up events.

This field is zero if Port Power() is zero.

This bit is output from the controller as signal pwrctl_wake_ovrcurr_en (host core only) for

use by an external power control circuit.