XC886/888CLM

Capture/Compare Unit 6

User’s Manual

14-92

V1.3, 2010-02

CCU6, V 1.0

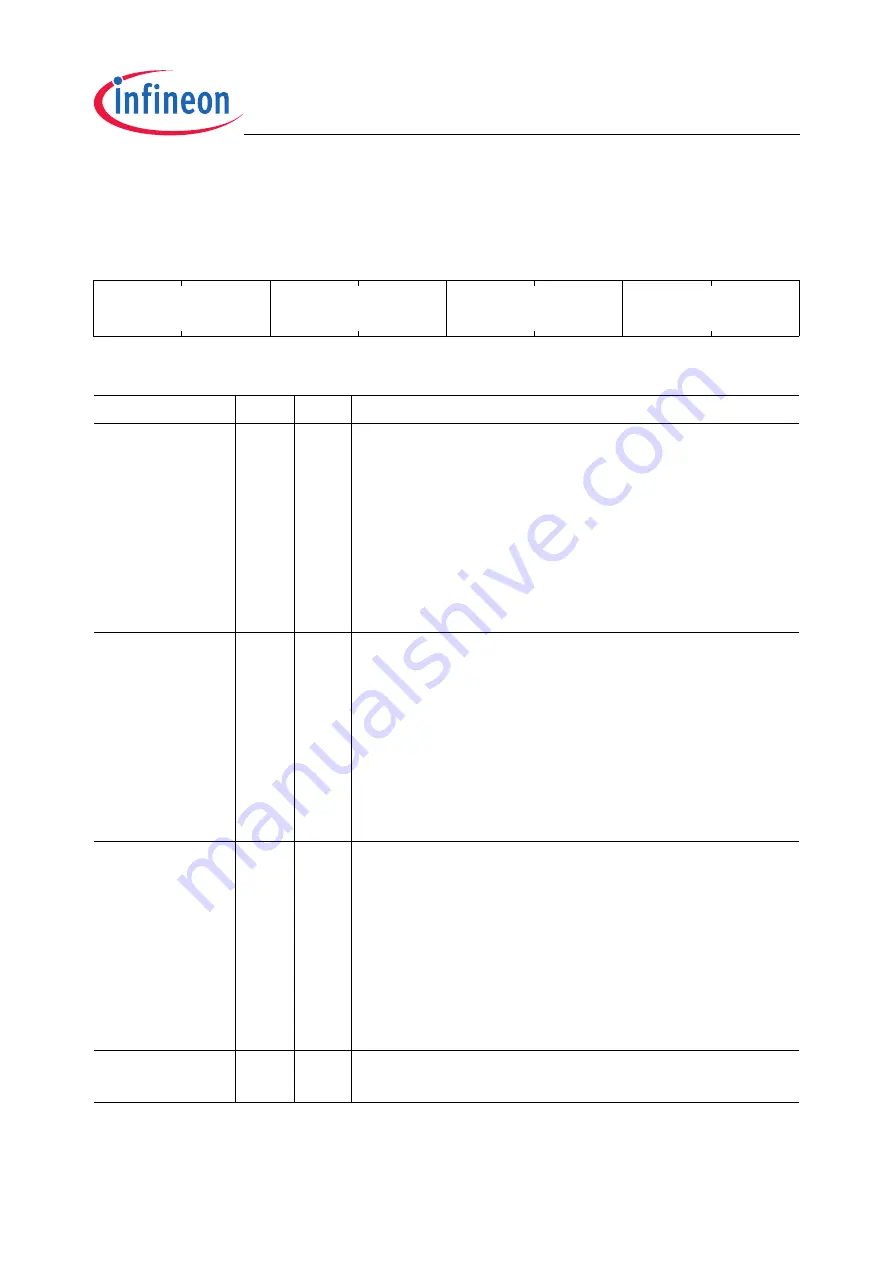

INPH

Capture/Compare Interrupt Node Pointer Register High

Reset Value: 39

H

7

6

5

4

3

2

1

0

0

INP

T13

INP

T12

INP

ERR

r

rw

rw

rw

Field

Bits

Type Description

INPERR

1:0

rw

Interrupt Node Pointer for Error Interrupts

This bit field defines the interrupt output line, which is

activated due to a set condition for bit TRPF (if enabled

by bit ENTRPF) or for bit WHE (if enabled by bit

ENWHE).

00

Interrupt output line SR0 is selected.

01

Interrupt output line SR1 is selected.

10

Interrupt output line SR2 is selected.

11

Interrupt output line SR3 is selected.

INPT12

3:2

rw

Interrupt Node Pointer for Timer T12 Interrupts

This bit field defines the interrupt output line, which is

activated due to a set condition for bit T12OM (if

enabled by bit ENT12OM) or for bit T12PM (if enabled

by bit ENT12PM).

00

Interrupt output line SR0 is selected.

01

Interrupt output line SR1 is selected.

10

Interrupt output line SR2 is selected.

11

Interrupt output line SR3 is selected.

INPT13

5:4

rw

Interrupt Node Pointer for Timer T13 Interrupts

This bit field defines the interrupt output line, which is

activated due to a set condition for bit T13CM (if

enabled by bit ENT13CM) or for bit T13PM (if enabled

by bit ENT13PM).

00

Interrupt output line SR0 is selected.

01

Interrupt output line SR1 is selected.

10

Interrupt output line SR2 is selected.

11

Interrupt output line SR3 is selected.

0

7:6

r

Reserved

Returns 0 if read; should be written with 0.

*

Содержание XC886CLM

Страница 1: ...User s Manual V1 3 2010 02 Microcontrollers 8 Bit XC886 888CLM 8 Bit Single Chip Microcontroller...

Страница 3: ...User s Manual V1 3 2010 02 Microcontrollers 8 Bit XC886 888CLM 8 Bit Single Chip Microcontroller...

Страница 324: ...XC886 888CLM Serial Interfaces User s Manual 12 52 V1 3 2010 02 Serial Interfaces V 1 0...

Страница 663: ...w w w i n f i n e o n c o m Published by Infineon Technologies AG...