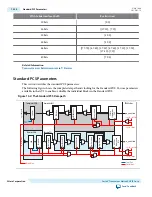

FPGA Fabric Interface Width

Bus Bits Used

10 bits

[9:0]

16 bits

{[17:10], [7:0]}

20 bits

[19:0]

40 bits

[39:0]

64 bits

{[77:70], [67:60], [57:50], [47:40], [37:30], [27:20],

[17:10], [7:0]}

80 bits

[79:0]

Related Information

Transceiver Architecture in Arria V Devices

Standard PCS Parameters

This section describes the standard PCS parameters.

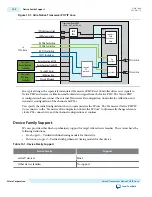

The following figure shows the complete datapath and clocking for the Standard PCS. You use parameters

available in the GUI to enable or disable the individual blocks in the Standard PCS.

Figure 13-2: The Standard PCS Datapath

Transmitter PCS

Transmitter PMA

Receiver PMA

Receiver PCS

FPGA Fabric

Byt

e O

rdering

RX Phase

Compensa

tion

FIFO

Byt

e D

eserializ

er

8B/10B D

ec

oder

Ra

te Ma

tch FIFO

W

or

d A

ligner

Deserializ

er

CDR

TX Phase

Compensa

tion

FIFO

Byt

e S

erializ

er

8B/10B E

nc

oder

TX B

it Slip

Serializ

er

rx_serial_da

ta

tx_serial_da

ta

tx_parallel data

rx_parallel data

/2

/2

tx_std_coreclkin

rx_std_coreclkin

Parallel Clock

Serial

Clock

Serial Clock

Parallel Clock

tx_std_clkout

rx_std_clkout

13-10

Standard PCS Parameters

UG-01080

2015.01.19

Altera Corporation

Arria V Transceiver Native PHY IP Core

Send Feedback