Simulation Support..................................................................................................................................15-34

Transceiver Reconfiguration Controller IP Core Overview............................ 16-1

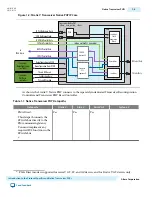

Transceiver Reconfiguration Controller System Overview................................................................. 16-2

Transceiver Reconfiguration Controller Performance and Resource Utilization............................16-5

Parameterizing the Transceiver Reconfiguration Controller IP Core............................................... 16-5

Parameterizing the Transceiver Reconfiguration Controller IP Core in Qsys................................. 16-6

General Options Parameters........................................................................................................ 16-6

Transceiver Reconfiguration Controller Interfaces.............................................................................. 16-8

MIF Reconfiguration Management Avalon-MM Master Interface........................................16-8

Transceiver Reconfiguration Interface....................................................................................... 16-9

Reconfiguration Management Interface...................................................................................16-10

Transceiver Reconfiguration Controller Memory Map.....................................................................16-12

Transceiver Reconfiguration Controller Calibration Functions.......................................................16-13

Offset Cancellation...................................................................................................................... 16-13

Duty Cycle Calibration............................................................................................................... 16-13

Auxiliary Transmit (ATX) PLL Calibration............................................................................ 16-14

Transceiver Reconfiguration Controller PMA Analog Control Registers.......................................16-14

Transceiver Reconfiguration Controller EyeQ Registers...................................................................16-16

EyeQ Usage Example...................................................................................................................16-19

Transceiver Reconfiguration Controller DFE Registers.................................................................... 16-20

Controlling DFE Using Register-Based Reconfiguration.................................................................. 16-22

Turning on DFE Continuous Adaptive mode.........................................................................16-22

Turning on Triggered DFE Mode............................................................................................. 16-23

Setting the First Tap Value Using DFE in Manual Mode...................................................... 16-23

Transceiver Reconfiguration Controller AEQ Registers....................................................................16-24

Transceiver Reconfiguration Controller ATX PLL Calibration Registers.......................................16-26

Transceiver Reconfiguration Controller PLL Reconfiguration.........................................................16-28

Transceiver Reconfiguration Controller PLL Reconfiguration Registers........................................16-30

Transceiver Reconfiguration Controller DCD Calibration Registers.............................................. 16-31

Transceiver Reconfiguration Controller Channel and PLL Reconfiguration.................................16-32

Channel Reconfiguration............................................................................................................16-33

PLL Reconfiguration................................................................................................................... 16-33

Transceiver Reconfiguration Controller Streamer Module Registers..............................................16-34

Mode 0 Streaming a MIF for Reconfiguration ....................................................................... 16-36

Mode 1 Avalon-MM Direct Writes for Reconfiguration.......................................................16-36

MIF Generation....................................................................................................................................... 16-37

Creating MIFs for Designs that Include Bonded or GT Channels................................................... 16-37

MIF Format.............................................................................................................................................. 16-38

xcvr_diffmifgen Utility............................................................................................................................16-39

Reduced MIF Creation............................................................................................................................16-42

Changing Transceiver Settings Using Register-Based Reconfiguration.......................................... 16-42

Register-Based Write...................................................................................................................16-42

Register-Based Read.................................................................................................................... 16-43

Changing Transceiver Settings Using Streamer-Based Reconfiguration.........................................16-43

Direct Write Reconfiguration.................................................................................................... 16-44

Streamer-Based Reconfiguration...............................................................................................16-45

Pattern Generators for the Stratix V and Arria V GZ Native PHYs.................................................16-46

Altera Transceiver PHY IP Core User Guide

TOC-9

Altera Corporation