Enabling the Standard PCS PRBS Verifier Using Streamer-Based Reconfiguration.........16-46

Enabling the Standard PCS PRBS Generator Using Streamer-Based Reconfiguration ....16-47

Enabling the 10G PCS PRBS Generator or Verifier Using Streamer-Based

Reconfiguration......................................................................................................................16-48

Disabling the Standard PCS PRBS Generator and Verifier Using Streamer-Based

Reconfiguration .....................................................................................................................16-50

Understanding Logical Channel Numbering...................................................................................... 16-50

Two PHY IP Core Instances Each with Four Bonded Channels.......................................... 16-53

One PHY IP Core Instance with Eight Bonded Channels.....................................................16-54

Two PHY IP Core Instances Each with Non-Bonded Channels...................................................... 16-55

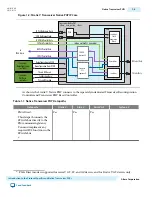

Transceiver Reconfiguration Controller to PHY IP Connectivity....................................................16-56

Merging TX PLLs In Multiple Transceiver PHY Instances...............................................................16-57

Sharing Reconfiguration Interface for Multi-Channel Transceiver Designs.................................. 16-58

Loopback Modes......................................................................................................................................16-58

Transceiver PHY Reset Controller IP Core......................................................17-1

Device Family Support for Transceiver PHY Reset Controller...........................................................17-3

Performance and Resource Utilization for Transceiver PHY Reset Controller ...............................17-3

Parameterizing the Transceiver PHY Reset Controller IP...................................................................17-4

Transceiver PHY Reset Controller Parameters..................................................................................... 17-4

Transceiver PHY Reset Controller Interfaces........................................................................................17-6

Timing Constraints for Bonded PCS and PMA Channels.................................................................17-10

Transceiver PLL IP Core for Stratix V, Arria V, and Arria V GZ Devices...... 18-1

Parameterizing the Transceiver PLL PHY............................................................................................. 18-3

Transceiver PLL Parameters.....................................................................................................................18-3

Transceiver PLL Signals............................................................................................................................18-4

Analog Parameters Set Using QSF Assignments..............................................19-1

Making QSF Assignments Using the Assignment Editor....................................................................19-1

Analog Settings for Arria V Devices....................................................................................................... 19-2

Analog Settings for Arria V Devices........................................................................................... 19-2

Analog Settings Having Global or Computed Values for Arria V Devices........................... 19-4

Analog Settings for Arria V GZ Devices...............................................................................................19-11

Analog Settings for Arria V GZ Devices...................................................................................19-11

Analog Settings Having Global or Computed Default Values for Arria V GZ Devices ... 19-14

Analog Settings for Cyclone V Devices................................................................................................ 19-26

XCVR_IO_PIN_TERMINATION............................................................................................19-26

XCVR_REFCLK_PIN_TERMINATION.................................................................................19-26

XCVR_TX_SLEW_RATE_CTRL............................................................................................. 19-27

XCVR_VCCR_ VCCT_VOLTAGE..........................................................................................19-27

Analog Settings Having Global or Computed Values for Cyclone V Devices....................19-27

Analog Settings for Stratix V Devices................................................................................................... 19-34

Analog PCB Settings for Stratix V Devices ............................................................................. 19-34

Analog Settings Having Global or Computed Default Values for Stratix V Devices ........19-38

TOC-10

Altera Transceiver PHY IP Core User Guide

Altera Corporation