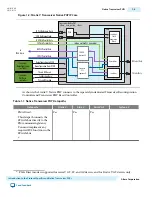

Figure 1-1: Transceiver PHY Top-Level Modules

To MAC

To HSSI Pins

Transceiver PHY

PMA

PCS

Customized functionality for:

10GBASE-R

10GBASE-KR

1G/10GBASE-R

XAUI

Interlaken

PCI Express PIPE

Avalon-ST

TX and RX

Avalon-MM

Control &

Status

PCS & PMA

Control & Status

Register Memory Map

S

Reset

Controller

S

Altera Transceiver

Reconfiguration

Controller

Offset Cancellation

Analog Settings

Avalon-MM PHY

Management

Read & Write

Control & Status

Registers

M

Avalon-MM master interface

M

S

Avalon-MM slave interface

S

PLL

CDR

Rx Deserializer

Tx Serializer

Embedded

Controller

Related Information

•

10GBASE-R PHY IP Core

on page 3-1

•

Backplane Ethernet 10GBASE-KR PHY IP Core Overview

•

1G/10 Gbps Ethernet PHY IP Core

on page 5-1

•

XAUI PHY IP Core

on page 6-1

•

Interlaken PHY IP Core

on page 7-1

•

PHY IP Core for PCI Express (PIPE)

on page 8-1

Native Transceiver PHYs

Each device family, beginning with Series V devices offers a separate Native PHY IP core to provide low-

level access to the hardware. There are separate IP Cores for Arria V, Arria V GZ, Cyclone V, and Stratix

V devices.

The Native PHYs allow you to customize the transceiver settings to meet your requirements. You can also

use the Native PHYs to dynamically reconfigure the PCS datapath. Depending on protocol mode selected,

built-in rules validate the options you specify. The following figure illustrates the Stratix V Native PHY.

1-2

Native Transceiver PHYs

UG-01080

2015.01.19

Altera Corporation

Introduction to the Protocol-Specific and Native Transceiver PHYs

Send Feedback