a.

PRBS TX Enable

, (0x97, bit[9])

b.

PRBS Pattern Select

, (0x97, bit[8:6])

7. Assert the channel reset to begin testing on the new PRBS pattern.

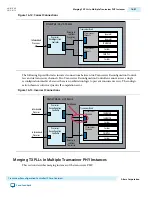

Enabling the 10G PCS PRBS Generator or Verifier Using Streamer-Based

Reconfiguration

Complete the following reads and writes to the Streamer module of the Transceiver Reconfiguration

Controller to enable one of the three pattern generators in the 10G PCS.

1. Read the Streamer Module

control and status

register

busy

bit (7’h3A, bit[8]) until it is clear.

2. Write the Streamer Module logical channel number to the Streamer

logical channel number

register at address 0x38.

3. Set the Streamer Module

control and status

register

Mode

bits (7’h3A, bits[3:2]) to Mode 1.

4. Write the pattern type (0x135 for the PRBS pattern generator or 0x15E for the PRBS pattern verifier)

to the Streamer Module

streamer offset

register at address 0x3B.

5. Write the Streamer Module

control and status

register (0x3A) with a value of 0x6 to initiate a read.

6. Read the Streamer Module

data

register at address 0x3C.

7. Perform a read-modify-write to the generator or verifier bits using the value read in step 6 to retain

values for the bits that should not change.

For example, to select the PRBS31 generator and to enable the PRBS generator, perform a read-

modify-write using the value 16'b0000-0-0-0-11-00 read from address 0x3C. In this 16-bit value, the

hyphens represent bits that should not be modified.

8. Write the new value from step 7 to the Streamer

data

register at address 0x3C

9. Write the Streamer

control and status

register (7'h3A) with a value of 0x5.

10.Repeat steps 3-9 to the

TX PRBS Clock Enable

(0x137) for

RX PRBS Clock Enable

(0x164).

11.Assert the channel resets.

Note: You can only enable one of the three pattern generators at a time.

Example 16-12: Enable the PRBS 31 Generator

//PRBS31 Pattern Generator selection and setup

read_32 0x3A //Read the control and status register busy

//bit[8] until it is clear

write_32 0x38 0x0 //write the logical channel to 0x38

write_32 0x3A 0x4 //set the MIF mode 1 to address 0x3A

write_32 0x3B 0x135 //write the pattern type offset

write_32 0x3A 0x6 //write the control and status register

//with a value of 0x6 to address 0x3A to initiate a read

//read_32 0x3C Read the value at address 0x3C

RMW {16'b0000-0-0-0-11-00, {Read_32 0x3C}} //Perform a

// read-modify-write with the generator or bits and the

// value read from above

write_32 0x3C 0x<result from above > //Write the new value from

//above to the dataregister at address 0x3C

write_32 0x3A0x5 //Write the control and status register

//with a value of 0x5 to address 0x3A

//Generator clock setup

read_32 0x3A //Read the control and status register busy

//bit[8] until it is clear

write_32 0x38 0x0 //write logical channel to 0x38

write_32 0x3A 0x4 //set the MIF mode 1 to address 0x3A

write_32 0x3B 0x137 //write the clock

16-48

Enabling the 10G PCS PRBS Generator or Verifier Using Streamer-Based

Reconfiguration

UG-01080

2015.01.19

Altera Corporation

Transceiver Reconfiguration Controller IP Core Overview

Send Feedback