Signal Name

Direction

Description

mode_1g_10gbar

Input

This signal indicates the requested mode for the

channel. A 1 indicates 1G mode and a 0 indicates

10G mode. This signal is only used when the

sequencer which performs automatic speed

detection is disabled.

en_lcl_rxeq

Output

This signal is not used. You can leave this

unconnected.

rxeq_done

Input

Link training requires RX equalization to be

complete. Tie this signal to 1 to indicate that RX

equalization is complete.

1G/10 Gbps Ethernet PHY IP Core

The 1G/10 Gbps Ethernet PHY MegaCore

®

(1G/10GbE) function allows you to instantiate both the

Standard PCS and the higher performance 10G PCS and a PMA. The Standard PCS implements the 1

GbE protocol as defined in Clause 36 of the

IEEE 802.3 2005 Standard

and also supports auto

-

negotiation

as defined in Clause 37 of the

IEEE 802.3 2005 Standard

standard. The 10G PCS implements the 10 Gb

Ethernet protocol as defined in

IEEE 802.3 2005 Standard

.

You can switch dynamically between the 1G and 10G PCS using the Altera Transceiver Reconfiguration

Controller IP Core to reprogram the core. This Ethernet core targets 1G/10GbE applications including

network interfaces to 1G/10GbE dual speed SFP+ pluggable modules, 1G/10GbE 10GBASE

-

T copper

external PHY devices to drive CAT

-

6/7 shielded twisted pair cables, and chip

-

to

-

chip interfaces.

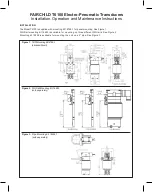

The following figure shows the top

-

level modules of the 1G/10GbE PHY IP Core. As this figure indicates,

the 1G/10 Gbps Ethernet PHY connects to a separately instantiated MAC. The 10G PCS receives and

transmits XGMII data. The Standard PCS receives and transmits GMII data. An Avalon Memory

-

Mapped

(Avalon

-

MM) slave interface provides access to PCS registers. the PMA receives and transmits serial data.

UG-01080

2015.01.19

1G/10 Gbps Ethernet PHY IP Core

5-27

1G/10 Gbps Ethernet PHY IP Core

Altera Corporation

Send Feedback