Preliminary

www.ti.com

Spinlock

1.14.3 Functional Description

1.14.3.1 Software Reset

The Spinlock module can be reset by software through the SPINLOCK_SYSCONFIG[1] SOFTRESET bit.

Setting this bit to 1 enables an active software reset that is functionally equivalent to a hardware reset.

This bit also indicates that the software reset is complete when its value is reset to 0. The software must

ensure that the software reset completes before doing Spinlock operations.

1.14.3.2 Power Management

describes power-management features available to the Spinlock module.

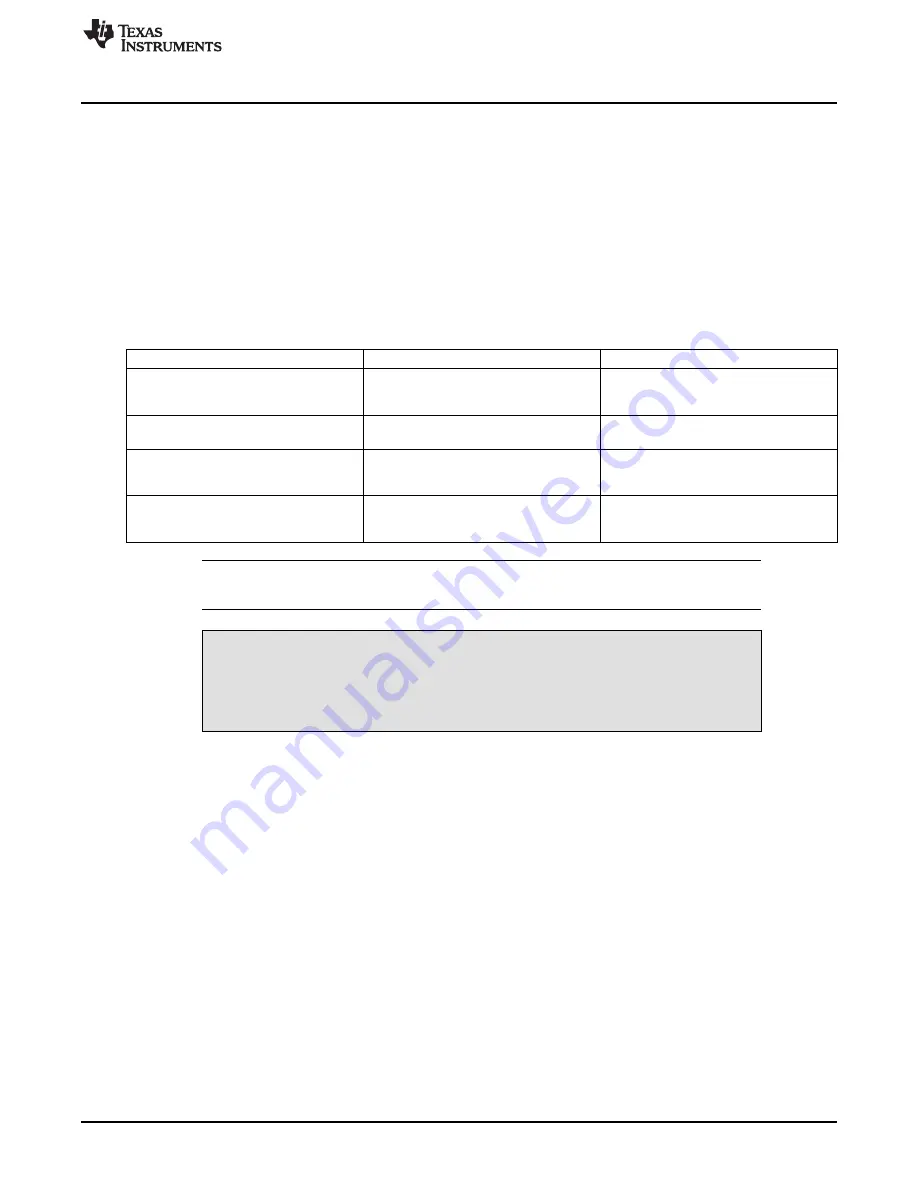

Table 1-114. Local Power Management Features

Feature

Registers

Description

Clock auto gating

[0] AUTOGATING bit

This bit indicates that the module uses an

automatic internal interface clock gating

strategy, based on interface activity.

Slave idle modes

[4:3] SIDLEMODE bit field

This bit field indicates that the module

uses smart-idle mode.

Clock activity

[8] CLOCKACTIVITY bit

This bit indicates that the interface clock is

not required by the module during idle

mode and may be switched off.

Global wake-up enable

[2] ENAWAKEUP bit

This bit indicates that the wake-up

generation feature (at module level) is

disabled.

NOTE:

All the local power management features are non-configurable (that is, their respective bits

or bit fields are read-only).

CAUTION

The PRCM module has no hardware means of reading CLOCKACTIVITY

settings. Thus, software must ensure consistent programming between the

CLOCKACTIVITY bit and Spinlock clock PRCM control bits.

The Spinlock module is normally idle, except when processing a request from its slave interface port. The

smart-idle mode acknowledges idle requests from the PRCM only when the module is prepared to go idle.

The Spinlock module is always ready to go idle if it does not have any request that it is processing.

The Spinlock module uses retention flops to retain state including the Taken state of each lock register.

This means that the module can be placed in retention at any time when it is not processing a request and

it is known that the system will not need to access the module.

Software must ensure to only power off the Spinlock module when no locks would be lost. In general, the

steps to powering down the Spinlock module are:

•

Check that all masters which might use the Spinlock module are either:

–

Already powered off

–

Notified that Spinlock is not available and the notification is acknowledged

•

If desired, check that no locks are currently held in the Spinlock module. The status of each bank of 64

locks can be read from the register. If any locks are held, they are orphaned because they are not held

by any master that is still active. Alternatively, you may decide to wait a timeout period to allow any

active master to clean up its locks before powering down.

•

The Spinlock module can now be powered off by writing the appropriate status to the PRCM.

In the case of powering off the whole system, these steps are unnecessary.

239

SPRUGX9 – 15 April 2011

Chip Level Resources

© 2011, Texas Instruments Incorporated

Содержание TMS320C6A816 Series

Страница 2: ...Preliminary 2 SPRUGX9 15 April 2011 Submit Documentation Feedback 2011 Texas Instruments Incorporated...

Страница 92: ...92 Read This First SPRUGX9 15 April 2011 Submit Documentation Feedback 2011 Texas Instruments Incorporated...

Страница 1122: ...1122 Multichannel Audio Serial Port McASP SPRUGX9 15 April 2011 Submit Documentation Feedback 2011 Texas Instruments Incorporated...

Страница 1562: ...1562 Real Time Clock RTC SPRUGX9 15 April 2011 Submit Documentation Feedback 2011 Texas Instruments Incorporated...

Страница 1658: ...1658 Timers SPRUGX9 15 April 2011 Submit Documentation Feedback 2011 Texas Instruments Incorporated...

Страница 1750: ...1750 UART IrDA CIR Module SPRUGX9 15 April 2011 Submit Documentation Feedback 2011 Texas Instruments Incorporated...

Страница 1984: ...1984 Universal Serial Bus USB SPRUGX9 15 April 2011 Submit Documentation Feedback 2011 Texas Instruments Incorporated...