Preliminary

Architecture

www.ti.com

11.2.8.5.14 Set the Receive Interrupt Mode (legacy only)

The RINTM bit field (SPCR1_REG[5:4]) determines which event generates a receive interrupt request

to the CPU. The receive interrupt (RINT) informs the CPU of changes to the serial port status. Four

options exist for configuring this interrupt.

•

RINTM = 00: RINT generated when the RRDY bit (SPCR1_REG[1]) changes from 0 to 1. Interrupt

on every serial word by tracking the RRDY bit in the SPCR1_REG register. Regardless of the value

of RINTM, RRDY can be read to detect the RRDY = 1 condition.

•

RINTM = 01: RINT generated by an end–of–frame condition in the receive multichannel selection

mode. In any other serial transfer case, this setting is not applicable and, therefore, no interrupts are

generated.

•

RINTM = 10: RINT generated by a new receive frame–synchronization pulse. Interrupt on detection

of receive frame–synchronization pulses. This generates an interrupt even when the receiver is in its

reset state. This is done by synchronizing the incoming frame–synchronization pulse to the CPU

clock and sending it to the CPU via RINT.

•

RINTM = 11: RINT generated when RSYNCERR is set. Interrupt on frame–synchronization error.

Regardless of the value of RINTM, RSYNCERR can be read to detect this condition

The McBSP provides also a common interrupt line McBSP.COMMONIRQ, which can be used by

setting the IRQENABLE register. All the above settings have equivalent enable bits in the IRQENABLE

register in order to enable the common interrupt line (RRDYEN is equivalent with RINTM = 00,

REOFEN is equivalent with RINTM = 01 (the interrupt is generated by an end-of-frame condition

regardless of the multichannel selection mode), RFSREN is equivalent with RINTM = 10 and

RSYNCERREN is equivalent with RINTM = 11 setting). This interrupt line has its own status register.

11.2.8.5.15 Set the Receive Frame-Sync Mode

FSRM bit (PCR_REG[10]), GSYNC bit (SRGR2_REG[15]), ALB bit (SPCR1_REG[15]) and DLB bit field

(XCCR_REG) are used to determine the source for receive frame synchronization and the function of

the McBSP.FSR pin.

shows how you can select various sources to provide the receive frame–synchronization

signal and the effect on the McBSP.FSR pin. The polarity of the signal on the McBSP.FSR pin is

determined by the FSRP bit.

In digital loop-back mode (DLB = 1), the transmit frame–synchronization signal is used as the receive

frame–synchronization signal.

Also in the analog loop back mode, the internal receive clock signal (CLKR), the internal receive

frame–synchronization signal (FSR) are internally connected to their transmit counterparts, CLKX and

FSX.

In the digital loop-back mode (DLB = 1) or analog loop-back mode (ALB = 1), the transmit frame

synchronization signal is used as the receive frame synchronization signal.

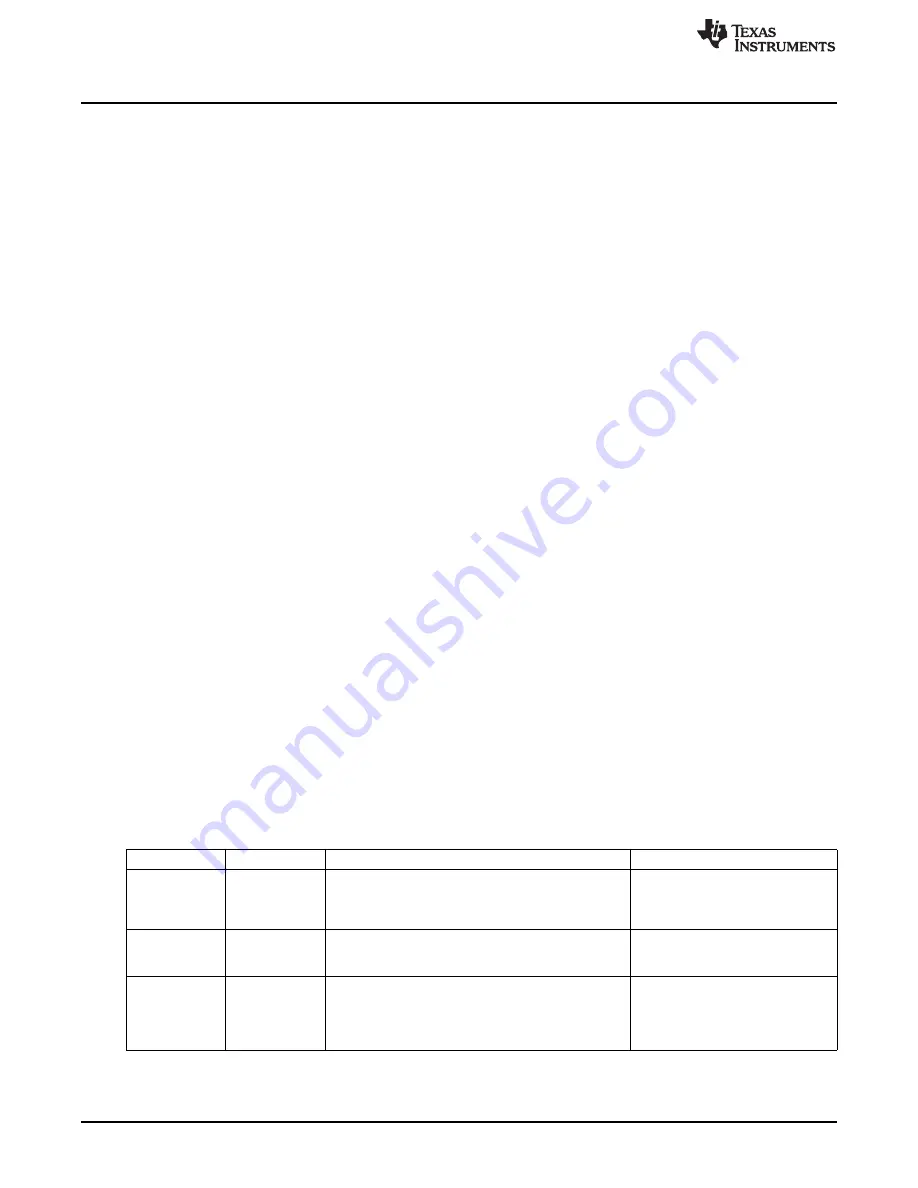

Table 11-13. FSRM and GSYNC Effects on Frame-Sync Signal and McBSP.FSR Pin

FSRM

GSYNC

Source of Receive Frame Synchronization

McBSP.FSR Pin Status

0

0 or 1

An external frame synchronization signal enters the

Input

McBSP through the McBSP.FSR pin. The signal is

then inverted as determined by FSRP before being

used as internal FSR.

1

0

Internal FSR is driven by the sample rate generator

Output. FSG is inverted as

frame–synchronization signal (FSG).

determined by FSRP before being

driven out on the McBSP.FSR pin.

1

1

Internal FSR is driven by the sample rate generator

Input. The external

frame–synchronization signal (FSG).

frame–synchronization input on the

McBSP.FSR pin is used to

synchronize CLKG and generate

FSG pulses.

1162Multichannel Buffered Serial Port (McBSP)

SPRUGX9 – 15 April 2011

© 2011, Texas Instruments Incorporated

Содержание TMS320C6A816 Series

Страница 2: ...Preliminary 2 SPRUGX9 15 April 2011 Submit Documentation Feedback 2011 Texas Instruments Incorporated...

Страница 92: ...92 Read This First SPRUGX9 15 April 2011 Submit Documentation Feedback 2011 Texas Instruments Incorporated...

Страница 1122: ...1122 Multichannel Audio Serial Port McASP SPRUGX9 15 April 2011 Submit Documentation Feedback 2011 Texas Instruments Incorporated...

Страница 1562: ...1562 Real Time Clock RTC SPRUGX9 15 April 2011 Submit Documentation Feedback 2011 Texas Instruments Incorporated...

Страница 1658: ...1658 Timers SPRUGX9 15 April 2011 Submit Documentation Feedback 2011 Texas Instruments Incorporated...

Страница 1750: ...1750 UART IrDA CIR Module SPRUGX9 15 April 2011 Submit Documentation Feedback 2011 Texas Instruments Incorporated...

Страница 1984: ...1984 Universal Serial Bus USB SPRUGX9 15 April 2011 Submit Documentation Feedback 2011 Texas Instruments Incorporated...