Serial peripheral interface / inter-IC sound (SPI/I2S)

RM0365

925/1080

DocID025202 Rev 7

The FRE flag is cleared when SPIx_SR register is read. If the ERRIE bit is set, an interrupt

is generated on the NSS error detection. In this case, the SPI should be disabled because

data consistency is no longer guaranteed and communications should be reinitiated by the

master when the slave SPI is enabled again.

30.5.12 NSS

pulse

mode

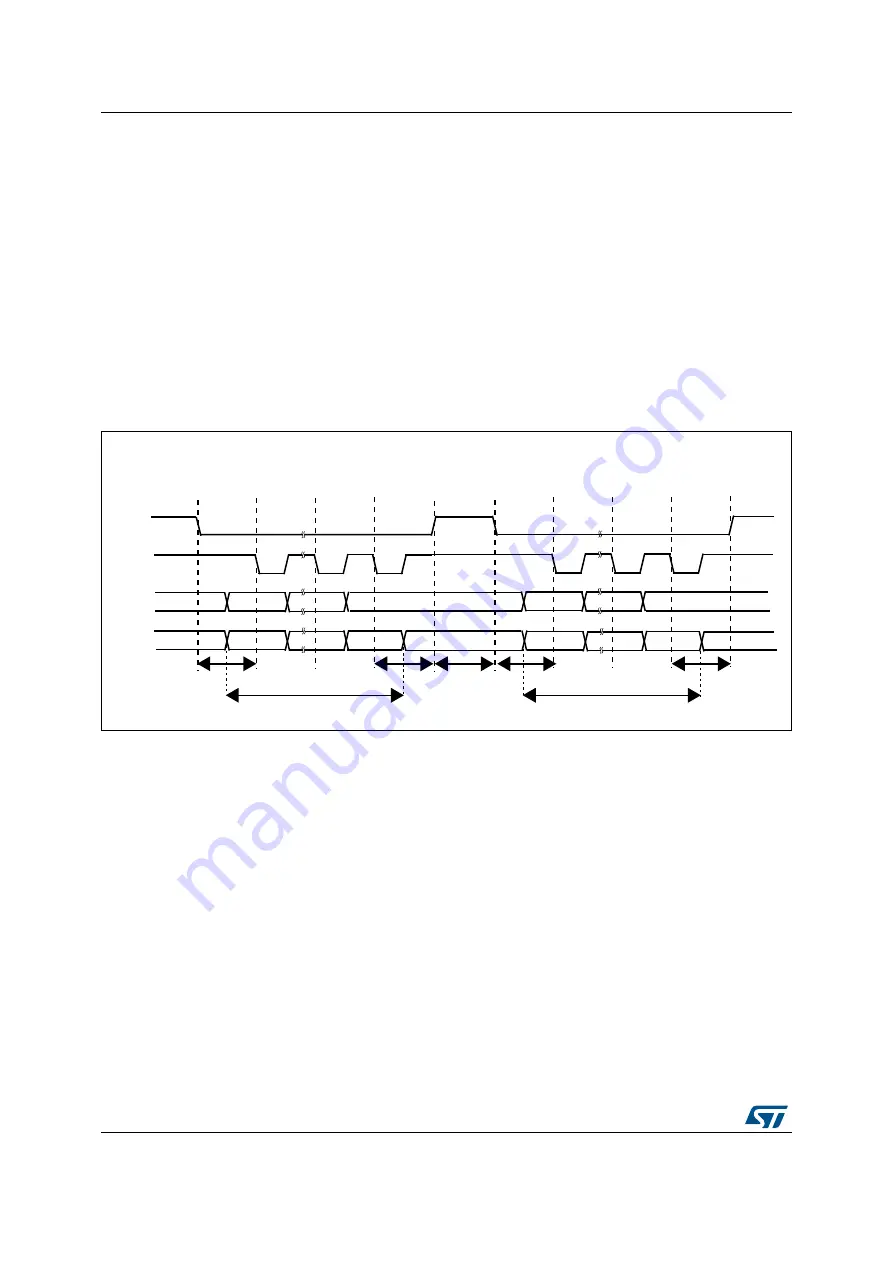

This mode is activated by the NSSP bit in the SPIx_CR2 register and it takes effect only if

the SPI interface is configured as Motorola SPI master (FRF=0) with capture on the first

edge (SPIx_CR1 CPHA = 0, CPOL setting is ignored). When activated, an NSS pulse is

generated between two consecutive data frame transfers when NSS stays at high level for

the duration of one clock period at least. This mode allows the slave to latch data. NSSP

pulse mode is designed for applications with a single master-slave pair.

illustrates NSS pin management when NSSP pulse mode is enabled.

Figure 354. NSSP pulse generation in Motorola SPI master mode

Note:

Similar behavior is encountered when CPOL = 0. In this case the sampling edge is the

rising

edge of SCK, and NSS assertion and deassertion refer to this sampling edge.

30.5.13 TI

mode

TI protocol in master mode

The SPI interface is compatible with the TI protocol. The FRF bit of the SPIx_CR2 register

can be used to configure the SPI to be compliant with this protocol.

The clock polarity and phase are forced to conform to the TI protocol requirements whatever

the values set in the SPIx_CR1 register. NSS management is also specific to the TI protocol

which makes the configuration of NSS management through the SPIx_CR1 and SPIx_CR2

registers (SSM, SSI, SSOE) impossible in this case.

In slave mode, the SPI baud rate prescaler is used to control the moment when the MISO

pin state changes to HiZ when the current transaction finishes (see

). Any baud

rate can be used, making it possible to determine this moment with optimal flexibility.

However, the baud rate is generally set to the external master clock baud rate. The delay for

the MISO signal to become HiZ (t

release

) depends on internal resynchronization and on the

069

026,

RXWSXW

166

RXWSXW

6&.

RXWSXW

VDPSOLQJ

0,62

LQSXW 'RQRWFDUH

06%

06%

ELWVWRELWV

'RQRWFDUH

/6%

/6%

06%

06%

/6%

/6%

ELWVWRELWV

'RQRWFDUH

0DVWHUFRQWLQXRXVWUDQVIHU&32/ &3+$ 1663

VDPSOLQJ VDPSOLQJ

VDPSOLQJ

VDPSOLQJ VDPSOLQJ

W

6&.

W

6&.

W

6&.

W

6&.

W

6&.