DocID025202 Rev 7

90/1080

RM0365

Peripheral interconnect matrix

96

7.3 Interconnection

details

7.3.1 DMA

interconnections

Hardware DMA requests are managed by peripherals. The DMA channels dedicated to

each peripheral are summarized in

Section 12.4.7: DMA request mapping

.

7.3.2

From ADC to ADC

ADC1 can be used as a "master" to trigger ADC2 "slave" start of conversion.

In dual ADC mode, the converted data of the master and slave ADCs can be read in

parallel.

A description of dual ADC mode is provided in

Section 15.3.29: Dual ADC modes

7.3.3

From ADC to TIM

ADC1 can provide trigger event through watchdog signals to advanced-control timers

(TIM1).

A description of the ADC analog watchdog settings is provided in

window watchdog (AWD1EN, JAWD1EN, AWD1SGL, AWD1CH, AWD2CH, AWD3CH,

AWD_HTx, AWD_LTx, AWDx)

.

The output (from ADC) is on signals ADC1_AWDx_OUT (x = 1..3 as there are 3 analog

watchdogs per ADC) and the input (to timer) on signal TIMx_ETR (external trigger).

TIMx_ETR is connected to ADC1_AWDx_OUT through bits in TIM1_OR registers; refer to

Section 20.4.21: TIM1 option registers (TIMx_OR)

LSE

-

-

-

-

-

-

-

-

-

-

-

-

x

-

-

-

-

-

-

LSI

-

-

-

-

-

-

-

-

-

-

-

-

x

-

-

-

-

-

-

MCO

-

-

-

-

-

-

-

-

-

-

-

-

x

-

-

-

-

-

-

RT

C

-

-

-

-

-

-

-

-

-

-

-

-

x

-

-

-

-

-

-

1. X means interconnect, and “-” means no interconnect.

2. Only in STM32F302xB/C/D/E.

3. Only in STM32F302xD/E.

4. Not in STM32F302xB/C.

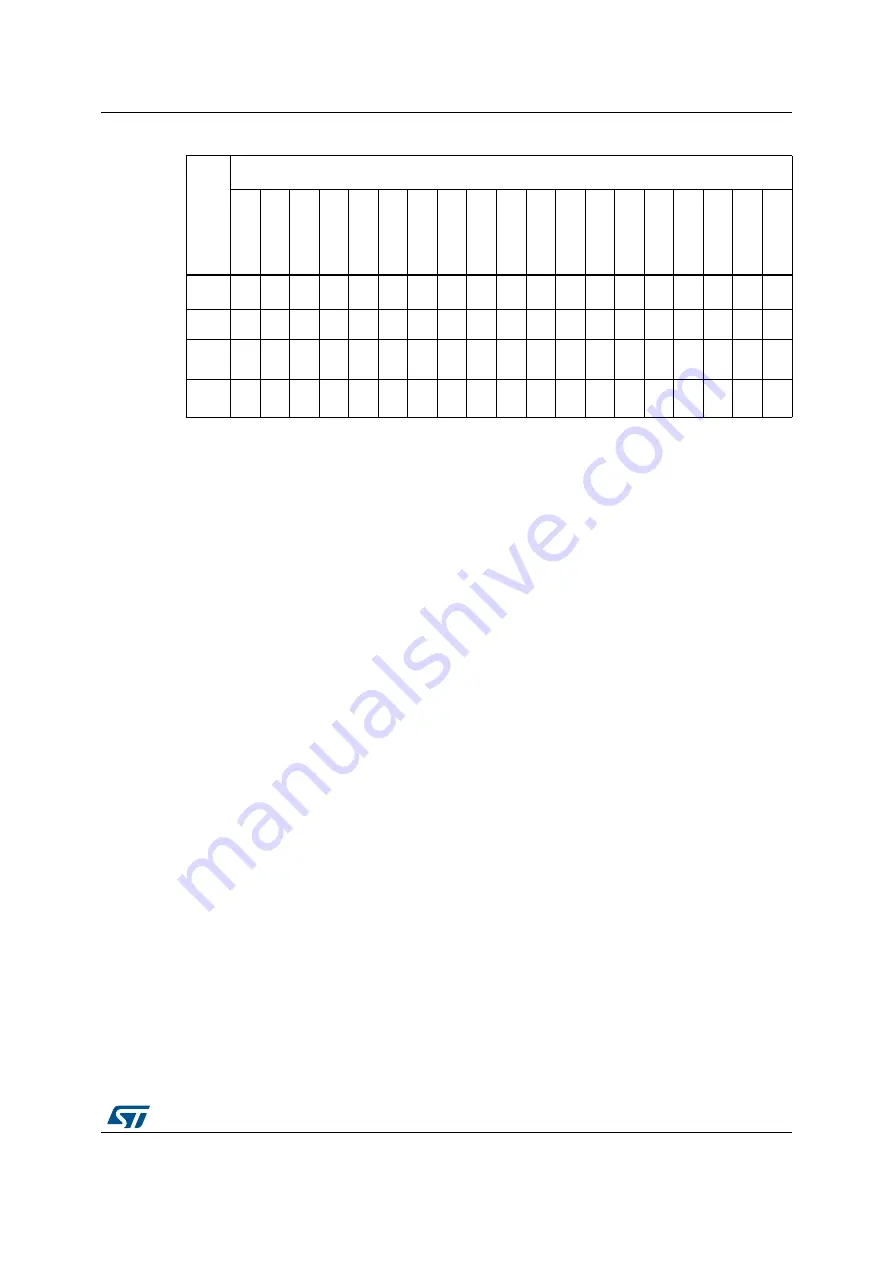

Table 16. STM32F302xx peripherals interconnect matrix

(1)

(continued)

Source

Destination

DMA1

DMA2

(2

)

ADC1

ADC2

(2)

COMP1

(2

)

CO

MP2

CO

MP4

CO

MP6

OP

AMP1

(2)

OP

AM

P2

TI

M1

TI

M15

TI

M16

TI

M17

TI

M2

TI

M3

(2)

TI

M4

(2)

DAC1

IRT

IM