RX610 Group

22. I

2

C Bus Interface (RIIC)

R01UH0032EJ0120 Rev.1.20

Page 735 of 1006

Feb 20, 2013

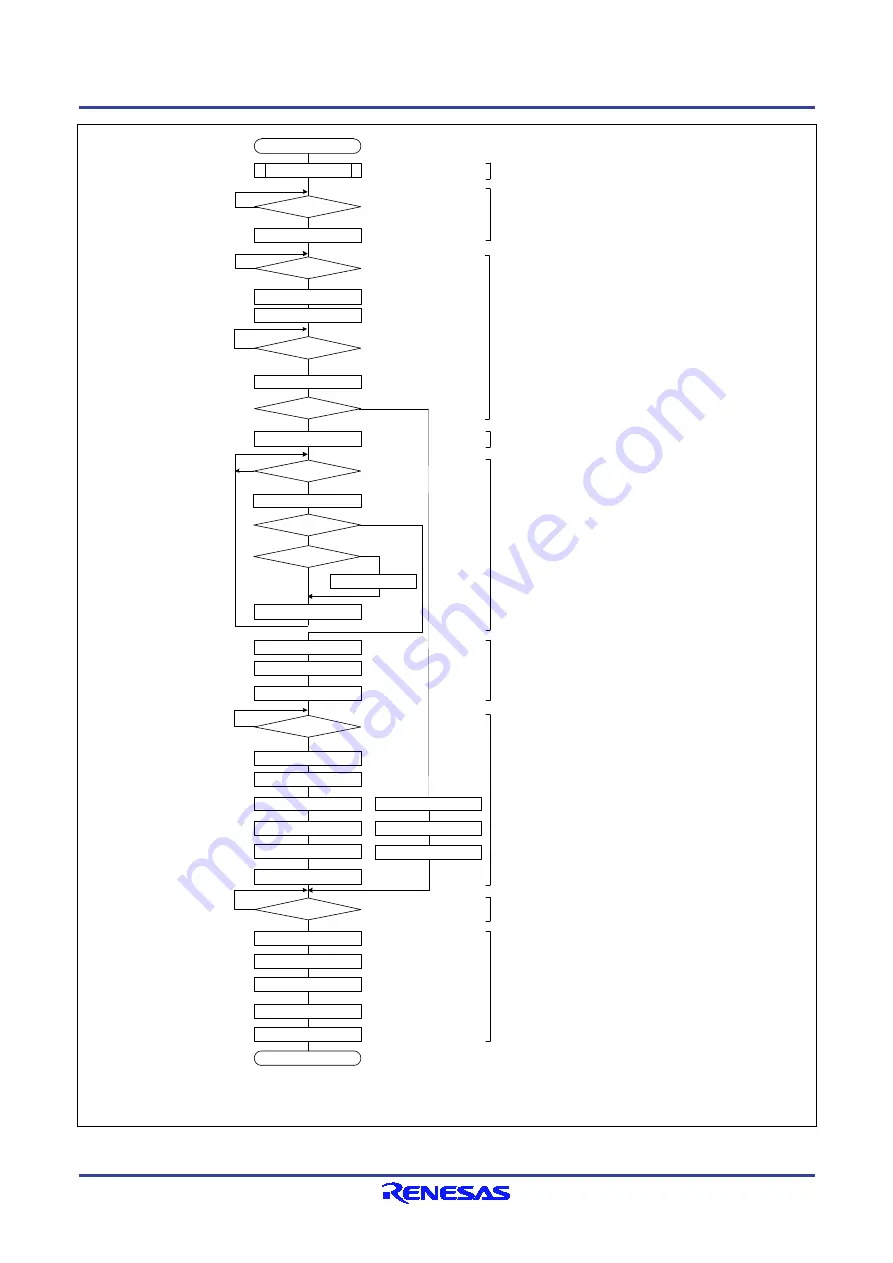

[3] Transmit slave address and R and check ACK.

No

Yes

[2] Check I

2

C bus occupation and issue a start

condition.

Yes

Yes

Master reception

ICCR2.ST = 1

Initial settings

No

Yes

Write data to ICDRT

Yes

No

ICSR2.NACKF = 0?

Yes

Perform dummy read of ICDRR

ICSR2.RDRF = 1?

Yes

Next data = final byte - 1?

No

Read ICDRR

Read ICDRR

No

No

ICSR2.STOP = 0

ICCR2.SP = 1

Read ICDRR

ICMR3.WAIT = 0

ICSR2.STOP = 0

ICCR2.SP = 1

Perform dummy read of ICDRR

ICSR2.STOP = 1?

No

TMOCNT = 0000h

ICMR3.RDRFS = 0

Yes

[1] Initial settings

[4] Perform dummy read.

[5] Read received data and prepare for receiving

final data.

[6] Change the timing of setting of the

RDRF, set the NACK, and read data of

(final byte – 1).

[7] Read final data and issue a stop

condition.

[8] Check stop condition issuance

[9] Processing for the next transfer operation

No

ICSR2.TDRE = 1?

ICSR2.RDRF = 1?

ICSR2.RDRF = 1?

ICCR2.BBSY = 0?

Next data = final byte - 2?

ICMR3.WAIT = 1

No

Yes

TMOCNT = 0000h

TMOCNT = 0000h

TMOCNT = 0000h

ICMR3.ACKBT = 1

ICMR3.ACKBT = 1

End of master reception

ICSR2.NACKF = 0

ICSR2.STOP = 0

ICMR3.ACKBT = 0

*1

*1

*1

*2

*2

TMOCNT = 0000h

*1

*1

*2

*2

Note 1: Internal counter for timeout

This is the case when the timeout function is in use

(this processing is not required if the function is not in use).

Note 2: Simultaneous writing is enabled.

ICMR3.RDRFS = 1

Figure 22.10 Example of Master Reception Flowchart (7-Bit Address Format)