RX610 Group

13. Data Transfer Controller (DTC)

R01UH0032EJ0120 Rev.1.20

Page 362 of 1006

Feb 20, 2013

13.5

DTC Setting Procedure

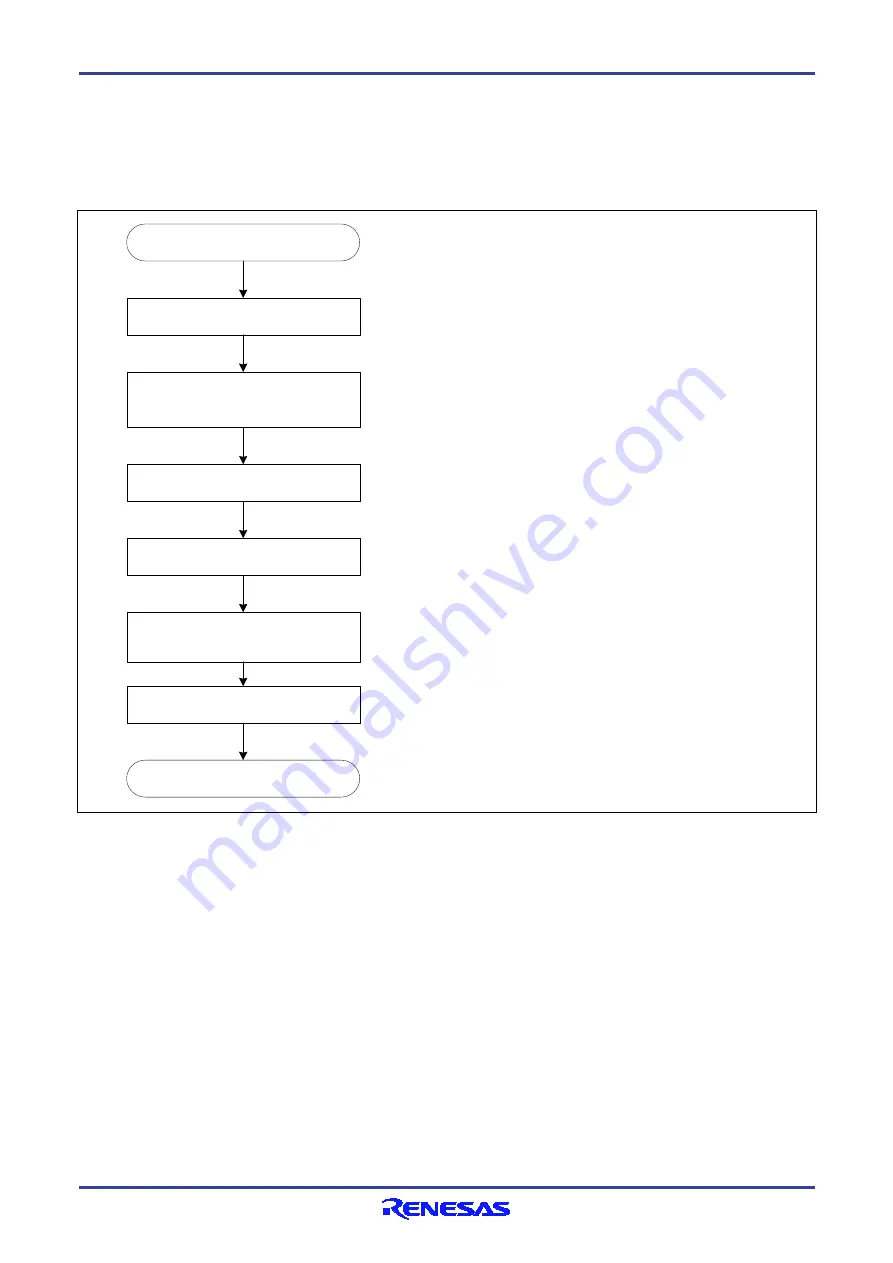

Figure 13.14 shows the procedure to set the DTC.

START

Set the RRS bit in DTCCR to 0

End

Set transfer data

(MRA, MRB, SAR, DAR, CRA, and CRB)

Set transfer data start addresses in the DTC

vector table

Set the RRS bit in DTCCR to 1

Set the ICU.IERi.IENj bit to 1.

Set the corresponding bits in ICU.ISELRi to 01b.

Set the interrupt source (to be a startup source)

enable bit to 1

[1]

[4]

[5]

[6]

[2]

[3]

[1]

Set ing the RRS bit in DTCCR to 0 resets the transfer data read skip

flag. After that, transfer data read is not skipped while the DTC is

activated.

When transfer data is updated, be sure to make this setting.

[2]

Allocate transfer data (MRA, MRB, SAR, DAR, CRA, and CRB) in the

data area. For setting transfer data, see section 13.2, Register

Description. For how to allocate transfer data, see section 13.3.1,

Allocating Transfer Data and DTC Vector Table.

[3]

Set transfer data start addresses in the DTC vector table. For how to

set the DTC vector table, see section 13.3.1, Allocating Transfer Data

and DTC Vector Table.

[4]

Set ing the RRS bit in DTCCR to 1 can skip the second and the

subsequent transfer data read cycles for continuous DTC activation

due to the same interrupt source. The RRS bit can always be set to 1,

but this setting during DTC transfer becomes valid from the next

transfer.

[5]

Set the ICU.IERi.IENj bit that corresponds to the DTC startup interrupt

to 1. Set the corresponding bits in ICU.ISELRi to 01b. For the

correspondence between interrupt sources and ISELRi register, see

table 13.3.

Note: To enable the DTC module, set the DTCST bit in DTCST to 1.

[6]

Set the interrupt source enable bit to be a startup source. When a

source interrupt is generated, he DTC is activated. For the setting of

the interrupt source enable bit, refer to the setting of the module that

is to be a startup source.

Figure 13.14 Procedure to Set the DTC