10-20

MPC8260 PowerQUICC II UserÕs Manual

MOTOROLA

Part III. The Hardware Interface

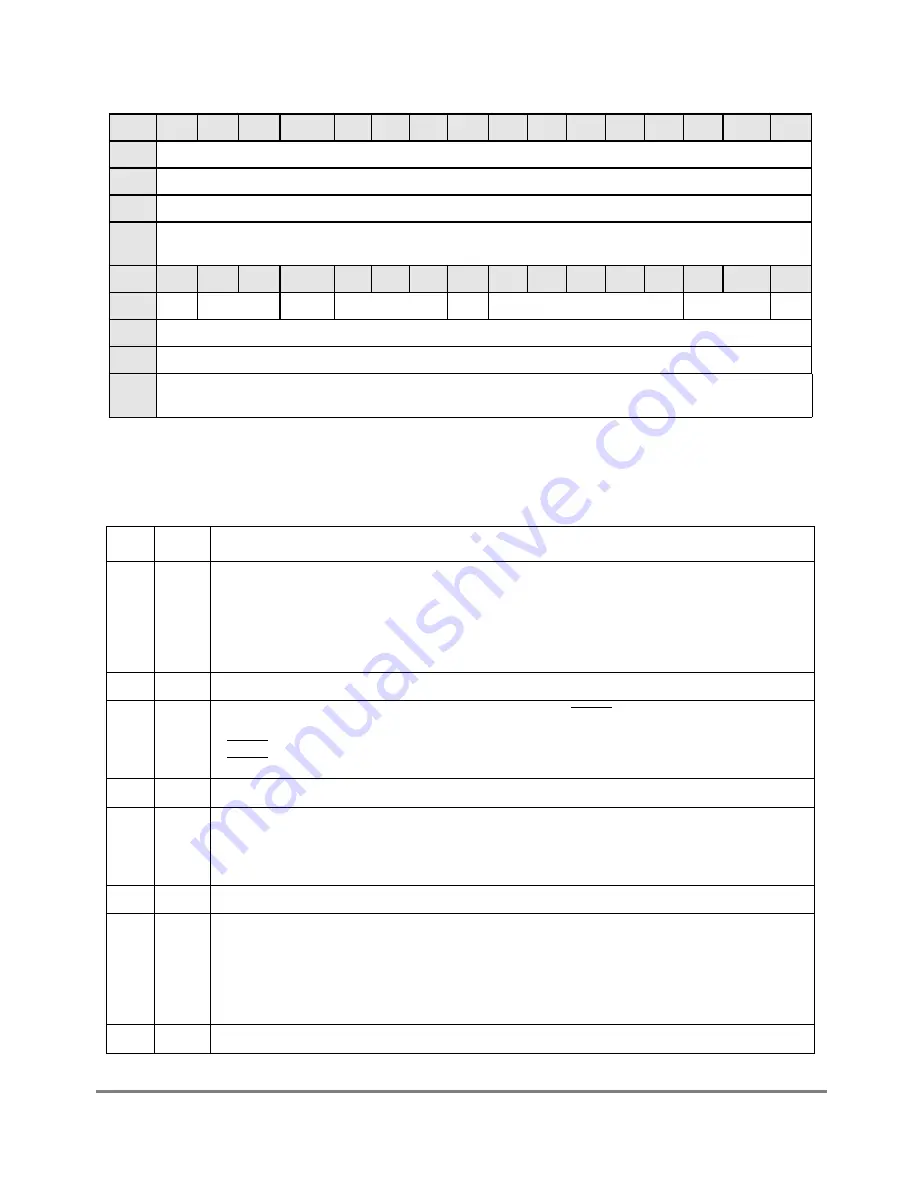

Figure 10-9 shows ORx as it is formatted for UPM mode.

Table 10-6 describes the OR

x

Þelds in UPM mode.

Bit

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

Field

AM

Reset 0000_0000_0000_0000

R/W

R/W

Addr

0x10104 (OR0); 0x1010C (OR1); 0x10114 (OR2); 0x1011C (OR3); 0x10124 (OR4); 0x1012C (OR5);

0x10134 (OR6); 0x1013C (OR7); 0x10144 (OR8); 0x1014C (OR9); 0x10154 (OR10); 0x1015C (OR11)

Bit

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

Field

AM

Ñ

BCTLD

Ñ

BI

Ñ

EHTR

Ñ

Reset

0000_0000_0000_0000

R/W

R/W

Addr

0x10106 (OR0); 0x1010E (OR1); 0x10116 (OR2); 0x1011E (OR3); 0x10126 (OR4); 0x1012E (OR5);

0x10136 (OR6); 0x1013E (OR7); 0x10146 (OR8); 0x1014E (OR9); 0x10156 (OR10); 0x1015E (OR11)

Figure 10-9. OR

x

ÑUPM Mode

Table 10-6. Option Register (OR

x

)ÑUPM Mode

Bits

Name Description

0Ð16

AM

Address mask. Provides masking for corresponding BR

x

bits. By masking address bits

independently, external devices of different size address ranges can be used. Any clear bit masks

the corresponding address bit. Any set bit causes the corresponding address bit to be used in the

comparison with the address pins. Address mask bits can be set or cleared in any order in the Þeld,

allowing a resource to reside in more than one area of the address map. AM can be read or written

at any time.

17Ð19

Ñ

Reserved, should be cleared.

19

BCTLD Data buffer control disable. Used to disable the assertion of BCTLx) during access to the current

memory bank. See Section 10.2.7, ÒData Buffer Controls (BCTLx)Ó.

0 BCTLx is asserted upon access to the current memory bank.

1 BCTLx is not asserted upon access to the current memory bank.

20Ð22

Ñ

Reserved, should be cleared.

23

BI

Burst inhibit. Indicates if this memory bank supports burst accesses.

0 The bank supports burst accesses

1 The bank does not support burst accesses. The UPMx executes burst accesses as series of single

accesses.

24Ð28

Ñ

Reserved, should be cleared.

29Ð30

EHTR

Extended hold time on read accesses. Indicates how many cycles are inserted between a read

access from the current bank and the next access.

00 Normal timing is generated by the memory controller. No additional cycles are inserted.

01 One idle clock cycle is inserted.

10 Four idle clock cycles are inserted.

11 Eight idle clock cycles are inserted.

31

Ñ

Reserved, should be cleared.

Содержание MPC8260 PowerQUICC II

Страница 1: ...MPC8260UM D 4 1999 Rev 0 MPC8260 PowerQUICC II UserÕs Manual ª ª ...

Страница 32: ...xxxii MPC8260 PowerQUICC II UserÕs Manual MOTOROLA CONTENTS Paragraph Number Title Page Number ...

Страница 66: ...lxvi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA ...

Страница 88: ...1 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Страница 120: ...2 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Страница 138: ...Part II iv MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II Configuration and Reset ...

Страница 184: ...4 46 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II ConÞguration and Reset ...

Страница 202: ...Part III vi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Страница 266: ...8 34 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Страница 382: ...10 106 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Страница 392: ...11 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Страница 430: ...Part IV viii MOTOROLA Part IV Communications Processor Module ...

Страница 490: ...14 36 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 524: ...17 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 556: ...18 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 584: ...19 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 632: ...21 24 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 652: ...22 20 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 668: ...23 16 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 758: ...27 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 780: ...28 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 874: ...29 94 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 920: ...31 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 980: ...A 4 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Appendixes ...

Страница 1002: ...Index 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA INDEX ...

Страница 1006: ......