4-26

MPC8260 PowerQUICC II UserÕs Manual

MOTOROLA

Part II. ConÞguration and Reset

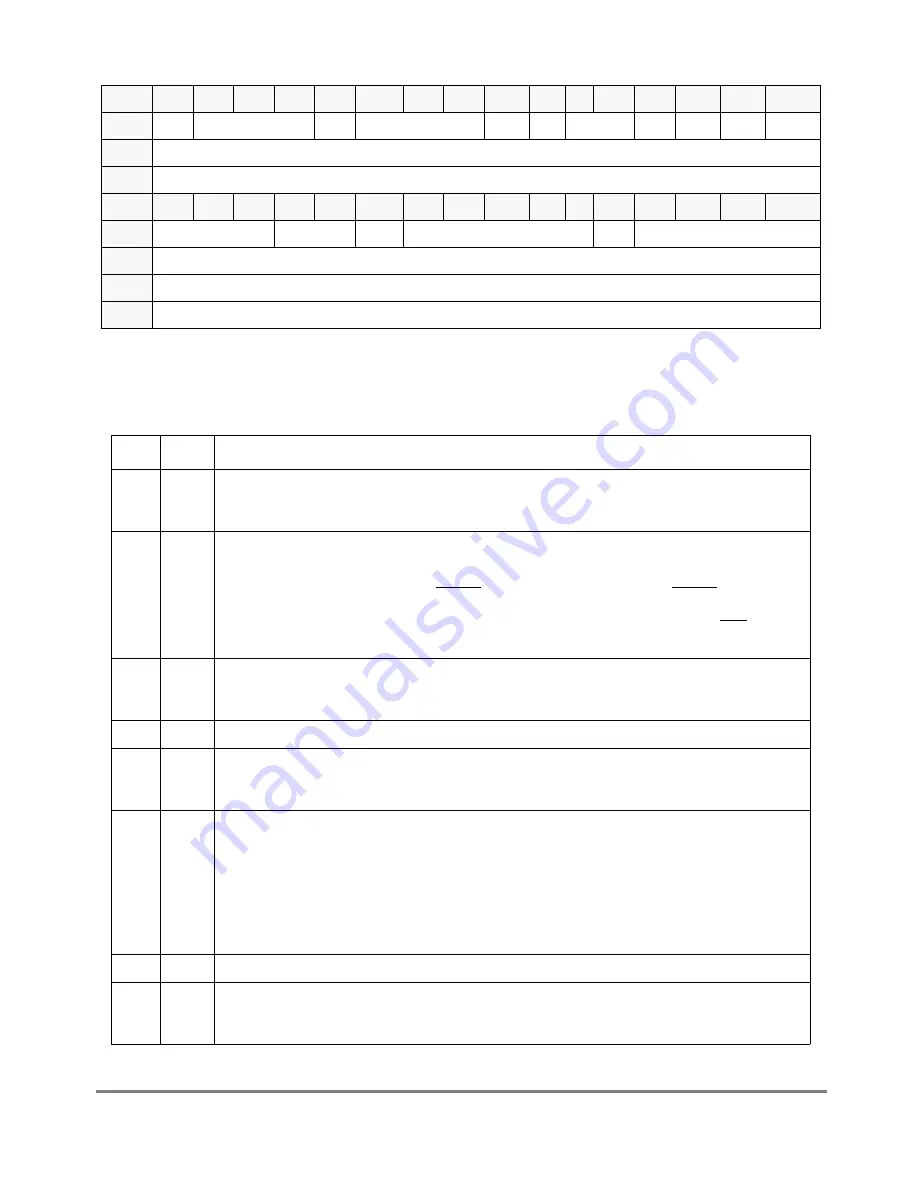

Table 4-9 describes BCR Þelds.

Bits

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

Field

EBM

APD

L2C

L2D

PLDP EAV

Ñ

ETM LETM EPAR LEPAR

Reset

Depends on reset conÞguration sequence. See Section 5.4.1, ÒHard Reset ConÞguration Word.Ó

R/W

R/W

Bits

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

Field

NPQM

Ñ

EXDD

Ñ

ISPS

Ñ

Reset

Depends on reset conÞguration sequence. See Section 5.4.1, ÒHard Reset ConÞguration Word.Ó

R/W

R/W

Addr

0x10024

Figure 4-21. Bus Configuration Register (BCR)

Table 4-9. BCR Field Descriptions

Bits

Name

Description

0

EBM

External bus mode.

0 Single MPC8260 bus mode is assumed

1 60x-compatible bus mode. For more information refer to Section 8.2, ÒBus ConÞguration.Ó

1Ð3

APD

Address phase delay. SpeciÞes the minimum number of address tenure wait states for address

operations initiated by a 60x bus master. BCR[APD] speciÞes the minimum number of address

tenure wait states for address operations initiated by 60x-bus devices. APD indicates how many

cycles the MPC8260 should wait for ARTRY, but because it is assumed that ARTRY can be

asserted (by other masters) only on cachable address spaces, APD is considered only on

transactions that hit one of the 60x-assigned memory controller banks and have the GBL signal

asserted during address phase.

4

L2C

Secondary cache controller. See Chapter 11, ÒSecondary (L2) Cache Support.Ó

0 No secondary cache controller is assumed.

1 An external secondary cache controller is assumed.

5Ð7

L2D

L2 cache hit delay. Controls the number of clock cycles from the assertion of TS until HIT is valid.

8

PLDP

Pipeline maximum depth. See Section 8.4.5, ÒPipeline Control.Ó

1 The pipeline maximum depth is zero.

0 The pipeline maximum depth is one.

9

EAV

Enable address visibility. Normally, when the MPC8260 is in single-MPC8260 bus mode, the bank

select signalsfor SDRAM accesses are multiplexed on the 60x bus address lines. So, for SDRAM

accesses, the internal address is not visible for debug purposes. However the bank select signals

can also be driven on dedicated pins (see SIUMCR[APPC]). In this case EAV can be used to force

address visibility.

0 Bank select signals are driven on 60x bus address lines. There is no full address visibility.

1 Bank select signals are not driven on address bus. During READ and WRITE commands to

SDRAM devices, the full address is driven on 60x bus address lines.

10Ð11

Ñ

Reserved, should be cleared.

12

ETM

Compatibility mode enable. See Section 8.4.3.8, ÒExtended Transfer Mode.Ó

0 Strict 60x bus mode. Extended transfer mode is disabled.

1 Extended transfer mode is enabled.

Содержание MPC8260 PowerQUICC II

Страница 1: ...MPC8260UM D 4 1999 Rev 0 MPC8260 PowerQUICC II UserÕs Manual ª ª ...

Страница 32: ...xxxii MPC8260 PowerQUICC II UserÕs Manual MOTOROLA CONTENTS Paragraph Number Title Page Number ...

Страница 66: ...lxvi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA ...

Страница 88: ...1 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Страница 120: ...2 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Страница 138: ...Part II iv MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II Configuration and Reset ...

Страница 184: ...4 46 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II ConÞguration and Reset ...

Страница 202: ...Part III vi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Страница 266: ...8 34 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Страница 382: ...10 106 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Страница 392: ...11 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Страница 430: ...Part IV viii MOTOROLA Part IV Communications Processor Module ...

Страница 490: ...14 36 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 524: ...17 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 556: ...18 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 584: ...19 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 632: ...21 24 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 652: ...22 20 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 668: ...23 16 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 758: ...27 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 780: ...28 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 874: ...29 94 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 920: ...31 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 980: ...A 4 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Appendixes ...

Страница 1002: ...Index 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA INDEX ...

Страница 1006: ......