31-2

MPC8260 PowerQUICC II UserÕs Manual

MOTOROLA

Part IV. Communications Processor Module

31.1 Key Features

Key features of the HDLC include the following:

¥

Flexible data buffers with multiple buffers per frame

¥

Separate interrupts for frames and buffers (receive and transmit)

¥

Received frames threshold to reduce interrupt overhead

¥

Four address comparison registers with masks

¥

Maintenance of four 16-bit error counters

¥

Flag/abort/idle generation and detection

¥

Zero insertion/deletion

¥

16- or 32-bit CRC-CCITT generation/checking

¥

Detection of nonoctet-aligned frames

¥

Detection of frames that are too long

¥

Programmable ßags (0Ð15) between successive frames

¥

External BD table

¥

Up to T3 rate

¥

Support of time stamp mode for Rx frames

¥

Support of nibble mode HDLC (4 bits per clocks)

31.2 HDLC Channel Frame Transmission Processing

The HDLC transmitter is designed to work with almost no core intervention. When the core

enables a transmitter, it starts sending ßags or idles as programmed in the HDLC mode

register (FPSMR). The HDLC controller polls the Þrst BD in the transmit channel BD table.

When there is a frame to transmit, the HDLC controller fetches the data (address, control,

and information) from the Þrst buffer and begins sending the frame after Þrst inserting the

user-speciÞed minimum number of ßags between frames. When the end of the current

buffer is reached and TxBD[L] (last buffer in frame) is set, the FCC appends the CRC (if

selected) and closing ßag. In HDLC, the lsb of each octet and the msb of the CRC are sent

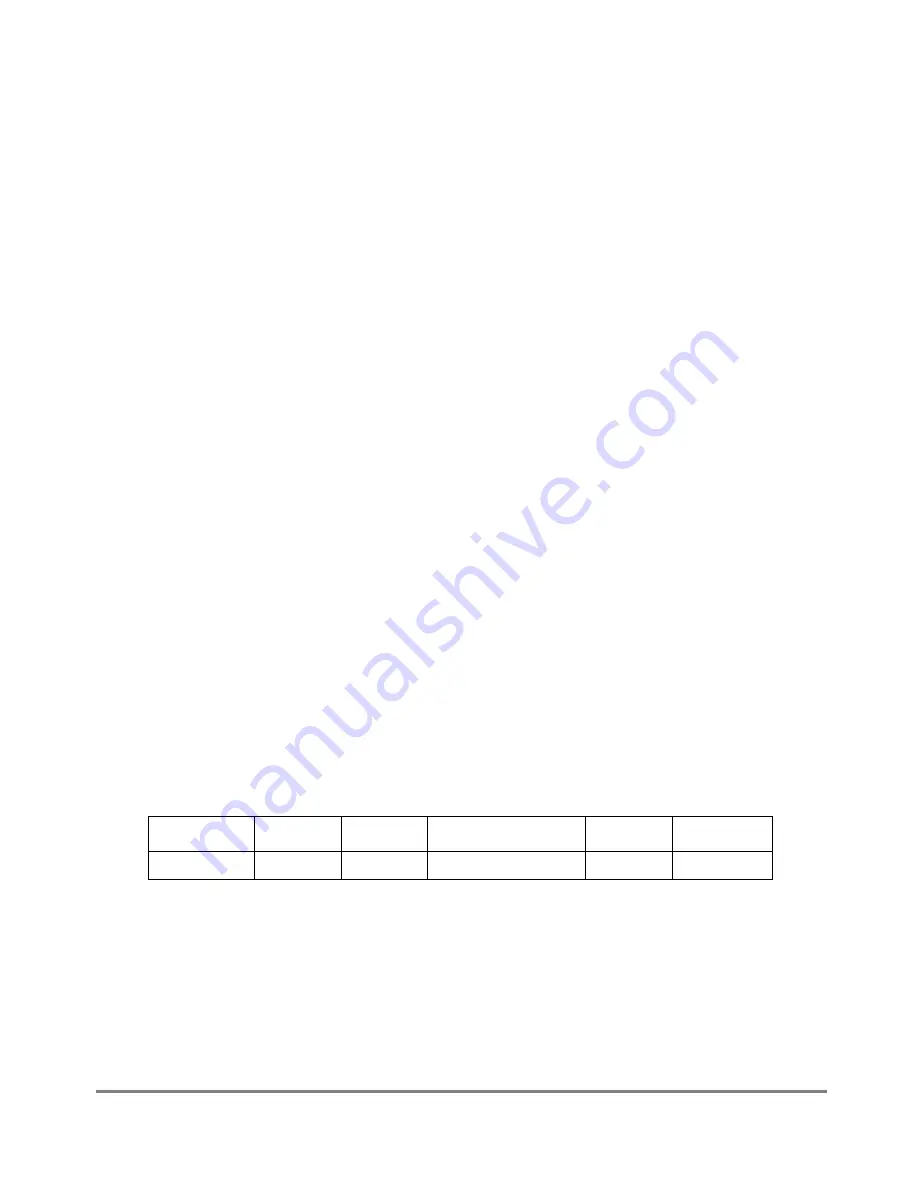

Þrst. Figure 31-1 shows a typical HDLC frame.

Figure 31-1. HDLC Framing Structure

After the closing ßag is sent, the HDLC controller writes the frame status bits into the BD

and clears the R bit. When the end of the current BD is reached and the L (last) bit is not

set (working in multibuffer mode), only the R bit is cleared. In either mode, an interrupt can

be issued if the I bit in the TxBD is set. The HDLC controller then proceeds to the next

TxBD in the table. In this way, the core can be interrupted after each buffer, after a speciÞc

buffer, after each frame, or after a number of frames.

Opening Flag

Address

Control

Information (Optional)

CRC

Closing Flag

8 Bits

16 Bits

8 Bits

8

n

Bits

16 Bits

8 Bits

Содержание MPC8260 PowerQUICC II

Страница 1: ...MPC8260UM D 4 1999 Rev 0 MPC8260 PowerQUICC II UserÕs Manual ª ª ...

Страница 32: ...xxxii MPC8260 PowerQUICC II UserÕs Manual MOTOROLA CONTENTS Paragraph Number Title Page Number ...

Страница 66: ...lxvi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA ...

Страница 88: ...1 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Страница 120: ...2 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Страница 138: ...Part II iv MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II Configuration and Reset ...

Страница 184: ...4 46 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II ConÞguration and Reset ...

Страница 202: ...Part III vi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Страница 266: ...8 34 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Страница 382: ...10 106 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Страница 392: ...11 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Страница 430: ...Part IV viii MOTOROLA Part IV Communications Processor Module ...

Страница 490: ...14 36 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 524: ...17 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 556: ...18 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 584: ...19 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 632: ...21 24 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 652: ...22 20 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 668: ...23 16 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 758: ...27 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 780: ...28 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 874: ...29 94 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 920: ...31 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 980: ...A 4 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Appendixes ...

Страница 1002: ...Index 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA INDEX ...

Страница 1006: ......