MOTOROLA

Chapter 31. FCC HDLC Controller

31-11

Part IV. Communications Processor Module

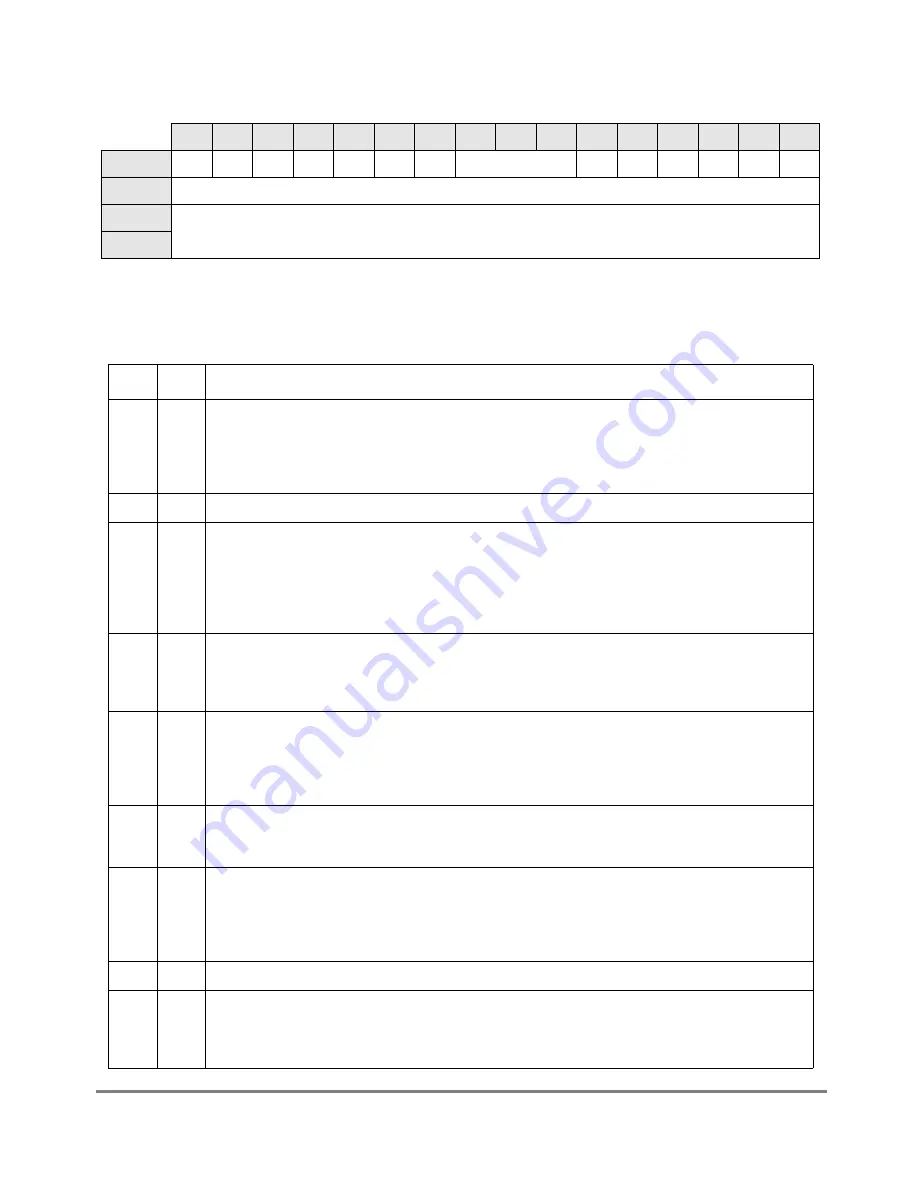

Figure 31-5 shows the FCC HDLC RxBD.

Table 31-7 describes RxBD Þelds.

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

0

E

Ñ

W

I

L

F

CM

Ñ

LG

NO

AB

CR

OV

CD

2

Data Length

4

Rx Data Buffer Pointer

6

Figure 31-5. FCC HDLC Receive Buffer Descriptor (RxBD)

Table 31-7. RxBD field Descriptions

Bits

Name

Description

0

E

Empty

0 The buffer is full with received data or data reception stopped because of an error. The core can

read or write to any Þelds of this RxBD. The CP does not use this BD while E = 0.

1 The buffer associated with this BD is empty. This RxBD and its associated receive buffer are

owned by the CP. Once E is set, the core should not write any Þelds of this RxBD.

1

Ñ

Reserved, should be cleared.

2

W

Wrap (Þnal BD in table)

0 Not the last BD in the RxBD table.

1 Last BD in the RxBD table. After this buffer is used, the CP receives incoming data into the Þrst

BD that RBASE points to in the table. The number of RxBDs in this table is programmable and is

determined only by the W bit and the overall space constraints of the dual-port RAM.

The RxBD table must contain more than one BD in HDLC mode.

3

I

Interrupt

0 The RXB bit is not set after this buffer is used, but RXF operation remains unaffected.

1 FCCE[RXB] or FCCE[RXF] is set when the HDLC controller uses this buffer. These two bits can

cause interrupts if they are enabled.

4

L

Last in frame. Set by the HDLC controller when this buffer is the last one in a frame. This implies the

reception of a closing ßag or reception of an error, in which case one or more of the CD, OV, AB, and

LG bits are set. The HDLC controller writes the number of frame octets to the data length Þeld.

0 Not the last buffer in a frame.

1 Last buffer in a frame.

5

F

First in frame. Set by the HDLC controller when this buffer is the Þrst in a frame.

0 Not the Þrst buffer in a frame.

1 First buffer in a frame.

6

CM

Continuous mode

0 Normal operation.

1 The E bit is not cleared by the CP after this BD is closed, allowing the associated data buffer to be

automatically overwritten the next time the CP accesses this BD. However, the E bit is cleared if

an error occurs during reception, regardless of the CM bit.

7Ð9

Ñ

Reserved, should be cleared.

10

LG

Rx frame length violation. A frame length greater than the maximum deÞned for this channel is

recognized, and only the maximum-allowed number of bytes (MFLR) is written to the data buffer. This

event is not reported until the RxBD is closed, the RXF bit is set, and the closing ßag is received. The

number of bytes received between ßags is written to the data length Þeld of this BD.

Содержание MPC8260 PowerQUICC II

Страница 1: ...MPC8260UM D 4 1999 Rev 0 MPC8260 PowerQUICC II UserÕs Manual ª ª ...

Страница 32: ...xxxii MPC8260 PowerQUICC II UserÕs Manual MOTOROLA CONTENTS Paragraph Number Title Page Number ...

Страница 66: ...lxvi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA ...

Страница 88: ...1 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Страница 120: ...2 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Страница 138: ...Part II iv MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II Configuration and Reset ...

Страница 184: ...4 46 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II ConÞguration and Reset ...

Страница 202: ...Part III vi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Страница 266: ...8 34 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Страница 382: ...10 106 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Страница 392: ...11 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Страница 430: ...Part IV viii MOTOROLA Part IV Communications Processor Module ...

Страница 490: ...14 36 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 524: ...17 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 556: ...18 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 584: ...19 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 632: ...21 24 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 652: ...22 20 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 668: ...23 16 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 758: ...27 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 780: ...28 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 874: ...29 94 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 920: ...31 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 980: ...A 4 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Appendixes ...

Страница 1002: ...Index 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA INDEX ...

Страница 1006: ......