2-12

MPC8260 PowerQUICC II UserÕs Manual

MOTOROLA

Part I. Overview

Table 2-1 shows the bit deÞnitions for HID0.

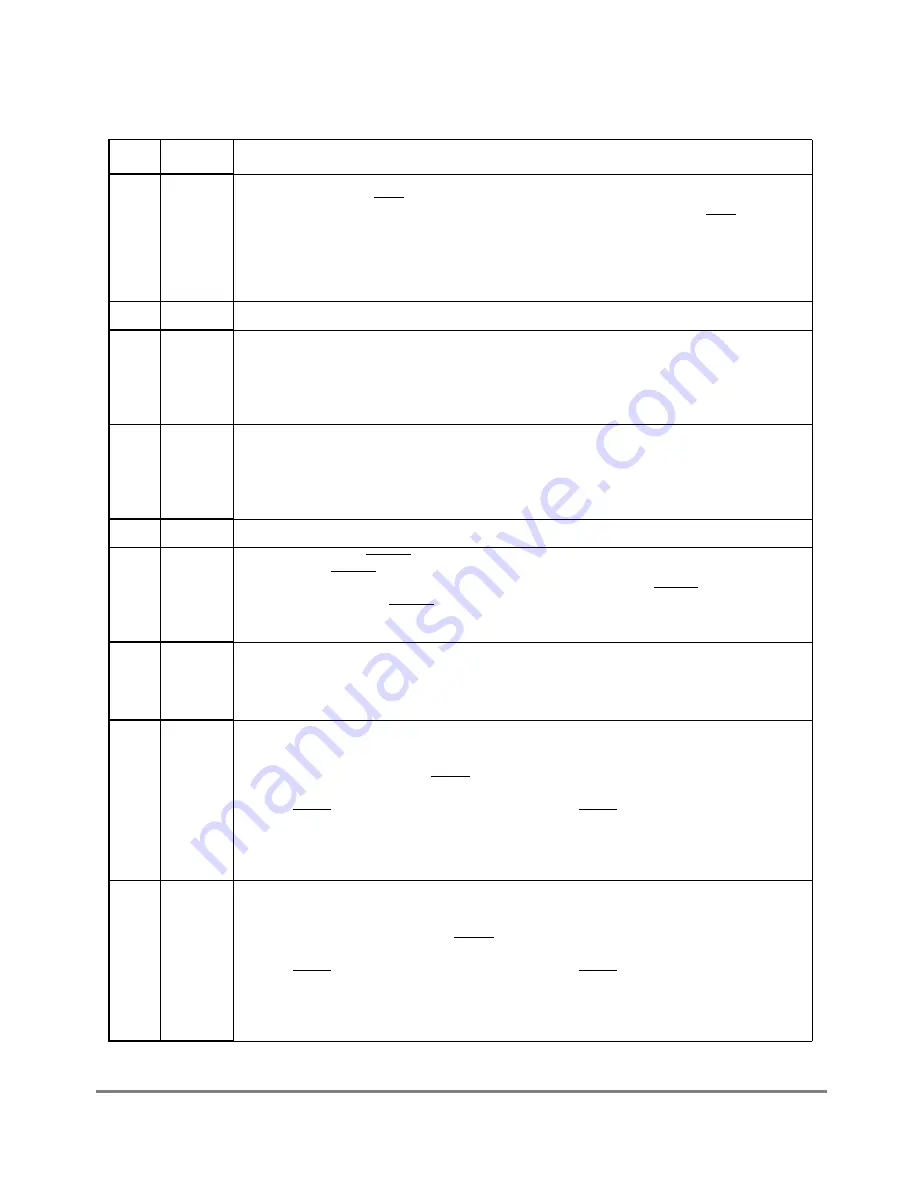

Table 2-1. HID0 Field Descriptions

Bits

Name

Description

0

EMCP

Enable machine check input pin

0 The assertion of the MCP does not cause a machine check exception.

1 Enables the entry into a machine check exception based on assertion of the MCP input,

detection of a Cache Parity Error, detection of an address parity error, or detection of a data

parity error.

Note that the machine check exception is further affected by MSR[ME], which speciÞes whether

the processor checkstops or continues processing.

1

Ñ

Reserved

2

EBA

Enable/disable 60x bus address parity checking

0 Prevents address parity checking.

1 Allows a address parity error to cause a checkstop if MSR[ME] = 0 or a machine check

exception if MSR[ME] = 1.

EBA and EBD let the processor operate with memory subsystems that do not generate parity.

3

EBD

Enable 60x bus data parity checking

0 Parity checking is disabled.

1 Allows a data parity error to cause a checkstop if MSR[ME] = 0 or a machine check exception

if MSR[ME] = 1.

EBA and EBD let the processor operate with memory subsystems that do not generate parity.

4Ð6

Ñ

Reserved

7

PAR

Disable precharge of ARTRY.

0 Precharge of ARTRY enabled

1 Alters bus protocol slightly by preventing the processor from driving ARTRY to high (negated)

state, allowing multiple ARTRY signals to be tied together. If this is done, the system must

restore the signals to the high state.

8

DOZE

Doze mode enable. Operates in conjunction with MSR[POW].

1

0 Doze mode disabled.

1 Doze mode enabled. Doze mode is invoked by setting MSR[POW] after this bit is set. In doze

mode, the PLL, time base, and snooping remain active.

9

NAP

Nap mode enable. Operates in conjunction with MSR[POW].

1

0 Nap mode disabled.

1 Nap mode enabled. Nap mode is invoked by setting MSR[POW] while this bit is set. When this

occurs, the processor asserts QREQ to indicate that it is ready to enter nap mode. If the

system logic determines that the processor may enter nap mode, the quiesce acknowledge

signal, QACK, is asserted back to the processor. Once QACK assertion is detected, the

processor enters nap mode after several processor clocks. Because bus snooping is disabled

for nap and sleep modes, this serves as a hardware mechanism for ensuring data coherency.

In nap mode, the PLL and the time base remain active.

10

SLEEP

Sleep mode enable. Operates in conjunction with MSR[POW].

1

0 Sleep mode disabled.

1 Sleep mode enabled. Sleep mode is invoked by setting MSR[POW] while this bit is set. When

this occurs, the processor asserts QREQ to indicate that it is ready to enter sleep mode. If the

system logic determines that the processor may enter sleep mode, the quiesce acknowledge

signal, QACK, is asserted back to the processor. Once QACK assertion is detected, the

processor enters sleep mode after several processor clocks. At this point, the system logic

may turn off the PLL by Þrst conÞguring PLL_CFG[0Ð3] to PLL bypass mode, and then

disabling SYSCLK.

Содержание MPC8260 PowerQUICC II

Страница 1: ...MPC8260UM D 4 1999 Rev 0 MPC8260 PowerQUICC II UserÕs Manual ª ª ...

Страница 32: ...xxxii MPC8260 PowerQUICC II UserÕs Manual MOTOROLA CONTENTS Paragraph Number Title Page Number ...

Страница 66: ...lxvi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA ...

Страница 88: ...1 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Страница 120: ...2 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Страница 138: ...Part II iv MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II Configuration and Reset ...

Страница 184: ...4 46 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II ConÞguration and Reset ...

Страница 202: ...Part III vi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Страница 266: ...8 34 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Страница 382: ...10 106 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Страница 392: ...11 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Страница 430: ...Part IV viii MOTOROLA Part IV Communications Processor Module ...

Страница 490: ...14 36 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 524: ...17 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 556: ...18 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 584: ...19 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 632: ...21 24 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 652: ...22 20 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 668: ...23 16 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 758: ...27 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 780: ...28 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 874: ...29 94 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 920: ...31 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 980: ...A 4 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Appendixes ...

Страница 1002: ...Index 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA INDEX ...

Страница 1006: ......