21-8

MPC8260 PowerQUICC II UserÕs Manual

MOTOROLA

Part IV. Communications Processor Module

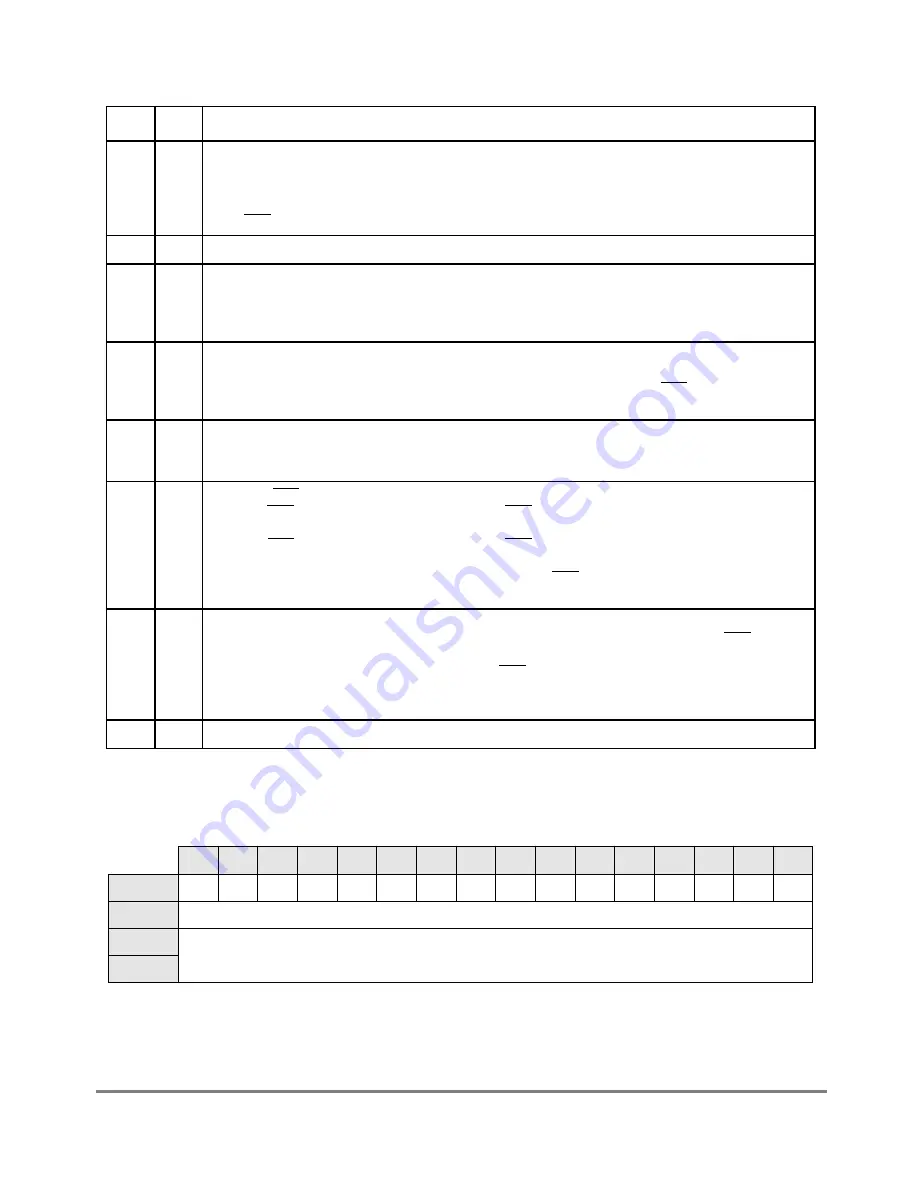

21.9 SCC HDLC Receive Buffer Descriptor (RxBD)

The CP uses the RxBD, shown in Figure 21-4, to report on data received for each buffer.

6

RTE

Retransmit enable.

0 No retransmission.

1 Automatic frame retransmission is enabled. Particularly useful in the HDLC bus protocol and ISDN

applications where multiple HDLC controllers can collide. Note that retransmission occurs only if a

lost CTS occurs on the Þrst or second buffer of the frame.

7

Ñ

Reserved, should be cleared.

8

FSE

Flag sharing enable. Valid only if GSMR_H[RTSM] = 1. Can be modiÞed on-the-ßy.

0 Normal operation.

1 If NOF[0Ð3] = 0b0000, a single shared ßag is sent between back-to-back frames. Other values of

NOF[0Ð3] are decremented by 1. Useful in signaling system #7 applications.

9

DRT

Disable receiver while transmitting.

0 Normal operation.

1 As the SCC sends data, the receiver is disabled and gated by the internal RTS. This helps if the

HDLC channel is on a multidrop line and the SCC does not need to receive its own transmission.

10

BUS

HDLC bus mode.

0 Normal HDLC operation.

1 HDLC bus operation is selected. See Section 21.14, ÒHDLC Bus Mode with Collision Detection.Ó

11

BRM

HDLC bus RTS mode. Valid only if BUS = 1. Otherwise, it is ignored.

0 Normal RTS operation during HDLC bus mode. RTS is asserted on the Þrst bit of the Tx frame and

negated after the Þrst collision bit is received.

1 Special RTS operation during HDLC bus mode. RTS is delayed by one bit with respect to the

normal case, which helps when the HDLC bus protocol is being run locally and sent over a long-

distance line at the same time. The one-bit delay allows RTS to be used to enable the transmission

line buffers so that the electrical effects of collisions are not sent over the transmission line.

12

MFF

Multiple frames in Tx FIFO. The receiver is not affected.

0 Normal operation. The Tx FIFO must never contain more than one HDLC frame. The CTS lost

status is reported accurately on a per-frame basis.

1 The Tx FIFO can hold multiple frames, but lost CTS may not be reported on the buffer/frame it

occurred on. This can improve performance of HDLC transmissions of small back-to-back frames or

when the number of ßags between frames should be limited.

13Ð15 Ñ

Reserved, should be cleared.

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

0

E

Ñ

W

I

L

F

CM

Ñ

DE

Ñ

LG

NO

AB

CR

OV

CD

2

Data Length

4

Rx Buffer Pointer

6

Figure 21-4. SCC HDLC Receive Buffer Descriptor (RxBD)

Table 21-6. PSMR HDLC Field Descriptions (Continued)

Bits

Name

Description

Содержание MPC8260 PowerQUICC II

Страница 1: ...MPC8260UM D 4 1999 Rev 0 MPC8260 PowerQUICC II UserÕs Manual ª ª ...

Страница 32: ...xxxii MPC8260 PowerQUICC II UserÕs Manual MOTOROLA CONTENTS Paragraph Number Title Page Number ...

Страница 66: ...lxvi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA ...

Страница 88: ...1 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Страница 120: ...2 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Страница 138: ...Part II iv MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II Configuration and Reset ...

Страница 184: ...4 46 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II ConÞguration and Reset ...

Страница 202: ...Part III vi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Страница 266: ...8 34 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Страница 382: ...10 106 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Страница 392: ...11 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Страница 430: ...Part IV viii MOTOROLA Part IV Communications Processor Module ...

Страница 490: ...14 36 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 524: ...17 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 556: ...18 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 584: ...19 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 632: ...21 24 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 652: ...22 20 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 668: ...23 16 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 758: ...27 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 780: ...28 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 874: ...29 94 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 920: ...31 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 980: ...A 4 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Appendixes ...

Страница 1002: ...Index 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA INDEX ...

Страница 1006: ......