MOTOROLA

Chapter 20. SCC UART Mode

20-19

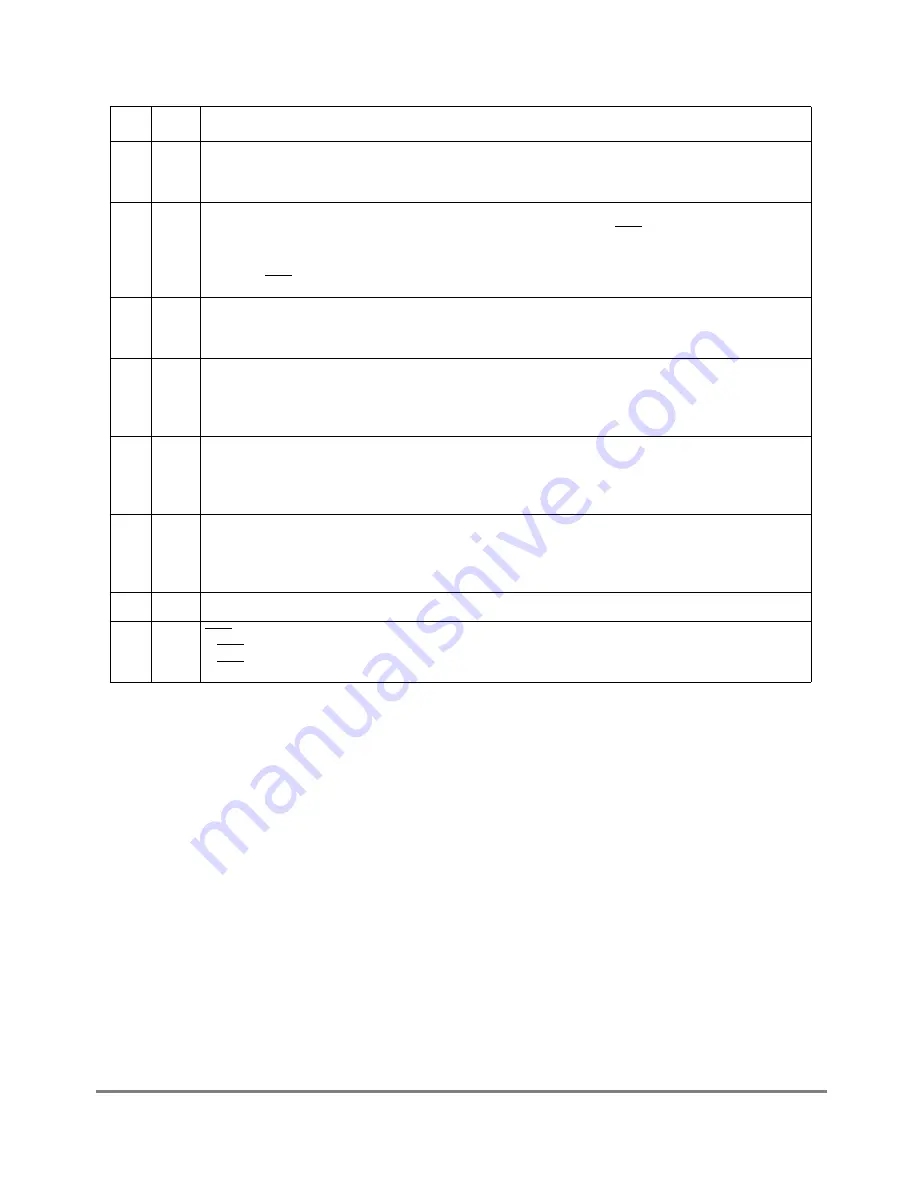

Part IV. Communications Processor Module

The data length and buffer pointer Þelds are described in Section 19.2, ÒSCC Buffer

Descriptors (BDs).Ó

20.19 SCC UART Event Register (SCCE) and Mask

Register (SCCM)

The SCC event register (SCCE) is used to report events recognized by the UART channel

and to generate interrupts. When an event is recognized, the controller sets the

corresponding SCCE bit. Interrupts can be masked in the UART mask register (SCCM),

which has the same format as SCCE. Setting a mask bit enables the corresponding SCCE

interrupt; clearing a bit masks it. Figure 20-10 shows example interrupts that can be

generated by the SCC UART controller.

3

I

Interrupt.

0 No interrupt is generated after this buffer is processed.

1 SCCE[TX] is set after this buffer is processed by the CPM, which can cause an interrupt.

4

CR

Clear-to-send report.

0 The next buffer is sent with no delay (assuming it is ready), but if a CTS lost condition occurs,

TxBD[CT] may not be set in the correct TxBD or may not be set at all. Asynchronous ßow control,

however, continues to function normally.

1 Normal CTS lost error reporting and three bits of idle are sent between consecutive buffers.

5

A

Address. Valid only in multidrop modeÑautomatic or manual.

0 This buffer contains only data.

1 This buffer contains address characters. All data in this buffer is sent as address characters.

6

CM

Continuous mode.

0 Normal operation. The CPM clears R after this BD is closed.

1 The CPM does not clear R after this BD is closed, allowing the buffer to be resent next time the

CPM accesses this BD. However, R is cleared by transmission errors, regardless of CM.

7

P

Preamble.

0 No preamble sequence is sent.

1 Before sending data, the controller sends an idle character consisting of all ones. If the data length

of this BD is zero, only a preamble is sent.

8

NS

No stop bit or shaved stop bit sent.

0 Normal operation. Stop bits are sent with all characters in this buffer.

1 If PSMR[SYN] = 1, data in this buffer is sent without stop bits. If SYN = 0, the stop bit is shaved,

depending on the DSR setting; see Section 20.14, ÒFractional Stop Bits (Transmitter).Ó

9Ð14 Ñ

Reserved, should be cleared.

15

CT

CTS lost. The CPM writes this status bit after sending the associated buffer.

0 CTS remained asserted during transmission.

1 CTS negated during transmission.

Table 20-11. SCC UART TxBD Status and Control Field Descriptions (Continued)

Bit

Name

Description

Содержание MPC8260 PowerQUICC II

Страница 1: ...MPC8260UM D 4 1999 Rev 0 MPC8260 PowerQUICC II UserÕs Manual ª ª ...

Страница 32: ...xxxii MPC8260 PowerQUICC II UserÕs Manual MOTOROLA CONTENTS Paragraph Number Title Page Number ...

Страница 66: ...lxvi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA ...

Страница 88: ...1 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Страница 120: ...2 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Страница 138: ...Part II iv MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II Configuration and Reset ...

Страница 184: ...4 46 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II ConÞguration and Reset ...

Страница 202: ...Part III vi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Страница 266: ...8 34 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Страница 382: ...10 106 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Страница 392: ...11 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Страница 430: ...Part IV viii MOTOROLA Part IV Communications Processor Module ...

Страница 490: ...14 36 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 524: ...17 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 556: ...18 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 584: ...19 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 632: ...21 24 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 652: ...22 20 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 668: ...23 16 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 758: ...27 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 780: ...28 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 874: ...29 94 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 920: ...31 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 980: ...A 4 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Appendixes ...

Страница 1002: ...Index 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA INDEX ...

Страница 1006: ......