6-4

MPC8260 PowerQUICC II UserÕs Manual

MOTOROLA

Part III. The Hardware Interface

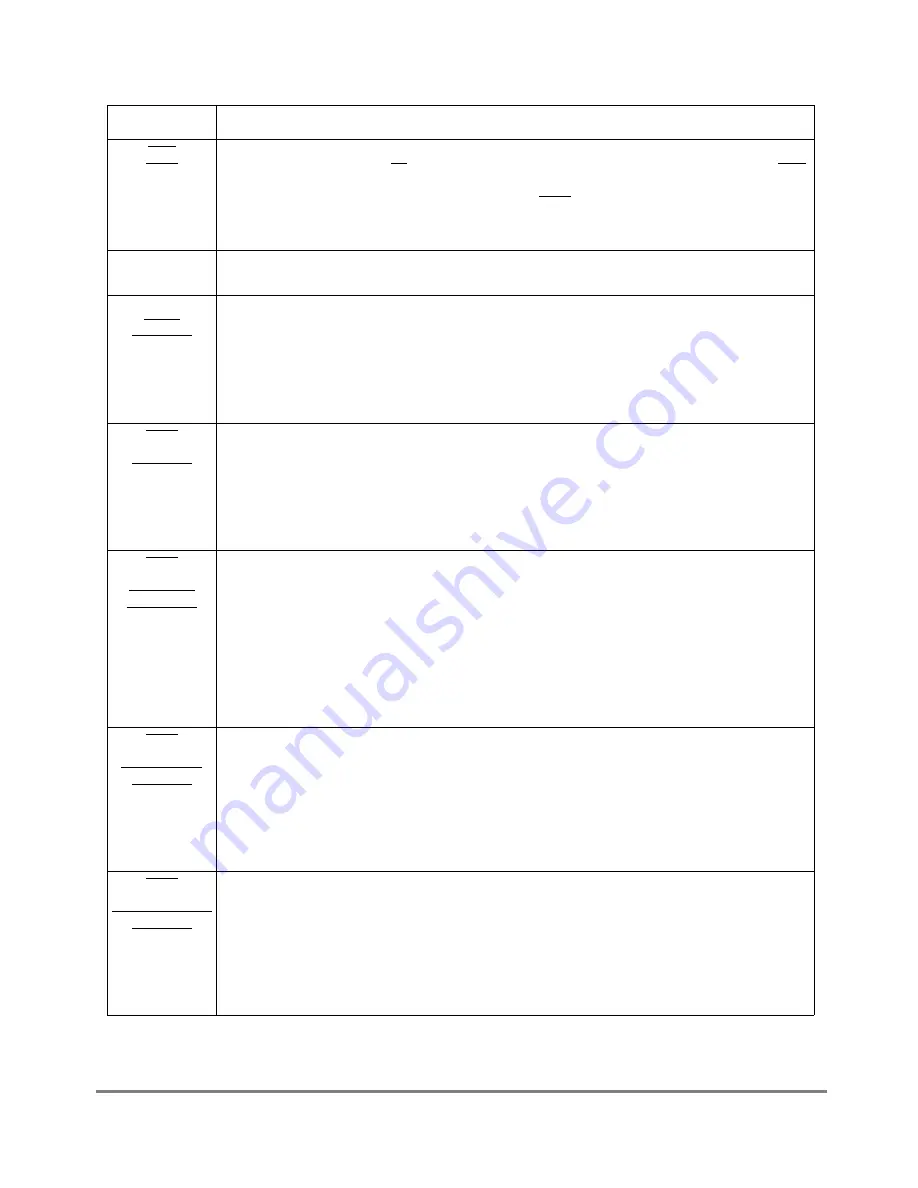

DBB

IRQ3

60x data bus busyÑ(Input/output)As an output the MPC8260 asserts this pin for the duration of the

data bus tenure. Following a TA, which terminates the data bus tenure, the MPC8260 negates DBB

for a fraction of a bus cycle and than stops driving this pin. As an input, the MPC8260 does not

assume 60x data bus ownership as long as it senses DBB asserted by an external 60x bus master.

Interrupt request 3ÑThis input is one of the eight external lines that can request (by means of the

internal interrupt controller) a service routine from the core.

D[0Ð63]

60x data busÑThese are input/output pins. In write transactions the 60x bus master drives the valid

data on this bus. In read transactions the 60x slave drives the valid data on this bus.

DP[0]

RSRV

EXT_BR2

60x data parity 0Ñ(Input/output)The 60x agent that drives the data bus drives also the data parity

signals. The value driven on data parity 0 pin should give odd parity (odd number of 1Õs) on the

group of signals that includes data parity 0 and D[0Ð7].

ReservationÑThe value driven on this output pin represents the state of the coherency bit in the

reservation address register that is used by the

lwarx

and

stwcx.

instructions.

External bus request 2Ñ(Input). An external master should assert this pin to request 60x bus

ownership from the internal arbiter.

IRQ1

DP[1]

EXT_BG2

Interrupt request 1ÑThis input is one of the eight external lines that can request (by means of the

internal interrupt controller) a service routine from the core.

60x data parity 1Ñ(Input/output)The 60x agent that drives the data bus drives also the data parity

signals. The value driven on data parity 1 pin should give odd parity (odd number of Ô1Õs) on the

group of signals that includes data parity 1 and D[8Ð15].

External bus grant 2Ñ(Output) The MPC8260 asserts this pin to grant 60x bus ownership to an

external bus master.

IRQ2

DP[2]

TLBISYNC

EXT_DBG2

Interrupt request 2ÑThis input is one of the eight external lines that can request (by means of the

internal interrupt controller) a service routine from the core.

60x data parity 2Ñ(Input/output)The 60x agent that drives the data bus drives also the data parity

signals. The value driven on data parity 2 pin should give odd parity (odd number of Ô1Õs) on the

group of signals that includes data parity 2 and S16Ð23].

TLB syncÑThis input pin can be used to synchronize 60x core instruction execution to hardware

indications. Asserting this pin will force the core to stop instruction execution following a

tlbsync

instruction execution. The core resumes instructions execution once this pin is negated.

External data bus grant 2Ñ(Output) The MPC8260 asserts this pin to grant 60x data bus ownership

to an external bus master.

IRQ3

DP[3]

CKSTP_OUT

EXT_BR3

Interrupt request 3ÑThis input is one of the eight external lines that can request (by means of the

internal interrupt controller) a service routine from the core.

60x data parity 3Ñ(Input/output)The 60x agent that drives the data bus drives also the data parity

signals. The value driven on data parity 3 pin should give odd parity (odd number of 1Õs) on the

group of signals that includes data parity 3 and D[24Ð31].

Checkstop outputÑ(Output) Assertion indicates that the core is in its checkstop mode.

External bus request 3Ñ(Input). An external master should assert this pin to request 60x bus

ownership from the internal arbiter.

IRQ4

DP[4]

CORE_SRESET

EXT_BG3

Interrupt request 4ÑThis input is one of the eight external lines that can request (by means of the

internal interrupt controller) a service routine from the core.

60x data parity 4Ñ(Input/output)The 60x agent that drives the data bus drives also the data parity

signals. The value driven on data parity 4 pin should give odd parity (odd number of Ô1Õs) on the

group of signals that includes data parity 4 and D[32Ð39].

Core system resetÑ(Input). Asserting this pin will force the core to branch to its reset vector.

External bus grant 3Ñ(Output) The MPC8260 asserts this pin to grant 60x bus ownership to an

external bus master.

Table 6-1. External Signals (Continued)

Signal Description

Содержание MPC8260 PowerQUICC II

Страница 1: ...MPC8260UM D 4 1999 Rev 0 MPC8260 PowerQUICC II UserÕs Manual ª ª ...

Страница 32: ...xxxii MPC8260 PowerQUICC II UserÕs Manual MOTOROLA CONTENTS Paragraph Number Title Page Number ...

Страница 66: ...lxvi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA ...

Страница 88: ...1 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Страница 120: ...2 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Страница 138: ...Part II iv MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II Configuration and Reset ...

Страница 184: ...4 46 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II ConÞguration and Reset ...

Страница 202: ...Part III vi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Страница 266: ...8 34 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Страница 382: ...10 106 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Страница 392: ...11 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Страница 430: ...Part IV viii MOTOROLA Part IV Communications Processor Module ...

Страница 490: ...14 36 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 524: ...17 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 556: ...18 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 584: ...19 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 632: ...21 24 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 652: ...22 20 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 668: ...23 16 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 758: ...27 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 780: ...28 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 874: ...29 94 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 920: ...31 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 980: ...A 4 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Appendixes ...

Страница 1002: ...Index 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA INDEX ...

Страница 1006: ......