MOTOROLA

Chapter 2. PowerPC Processor Core

2-27

Part I. Overview

2.6.1 PowerPC MMU Model

The primary functions of the MMU are to translate logical (effective) addresses to physical

addresses for memory accesses, and to provide access protection on blocks and pages of

memory.

There are two types of accesses generated by the processor core that require address

translationÑinstruction accesses and data accesses to memory generated by load and store

instructions.

The PowerPC MMU and exception models support demand-paged virtual memory. Virtual

memory management permits execution of programs larger than the size of physical

memory; demand-paged implies that individual pages are loaded into physical memory

from system memory only when they are Þrst accessed by an executing program.

The PowerPC architecture supports the following three translation methods:

¥

Address translations disabled. Translation is enabled by setting bits in the MSRÑ

MSR[IR] enables instruction address translations and MSR[DR] enables data

address translations. Clearing these bits disables translation and the effective address

is used as the physical address.

¥

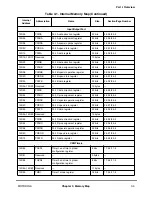

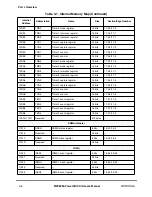

Block address translation. The PowerPC architecture deÞnes independent four-entry

BAT arrays for instructions and data that maintain address translations for blocks of

memory. Block sizes range from 128 Kbyte to 256 Mbyte and are software

selectable. The BAT arrays are maintained by system software. The BAT registers,

deÞned by the PowerPC architecture for block address translations, are shown in

Figure 2-2.

¥

Demand page mode. The page table contains a number of page table entry groups

(PTEGs). A PTEG contains eight page table entries (PTEs) of eight bytes each;

therefore, each PTEG is 64 bytes long. PTEG addresses are entry points for table

search operations.

The hashed page table is a variable-sized data structure that deÞnes the mapping

between virtual page numbers and physical page numbers. The page table size is a

power of 2, and its starting address is a multiple of its size.

On-chip instruction and data TLBs provide address translation in parallel with the

on-chip cache access, incurring no additional time penalty in the event of a TLB hit.

A TLB is a cache of the most recently used page table entries. Software is

responsible for maintaining the consistency of the TLB with memory. In the

MPC8260, the processor coreÕs TLBs are 64-entry, two-way set-associative caches

that contain instruction and data address translations. The MPC8260Õs core provides

hardware assist for software table search operations through the hashed page table

on TLB misses. Supervisor software can invalidate TLB entries selectively.

The MMU also directs the address translation and enforces the protection hierarchy

programmed by the operating system in relation to the supervisor/user privilege level of the

access and in relation to whether the access is a load or store.

Содержание MPC8260 PowerQUICC II

Страница 1: ...MPC8260UM D 4 1999 Rev 0 MPC8260 PowerQUICC II UserÕs Manual ª ª ...

Страница 32: ...xxxii MPC8260 PowerQUICC II UserÕs Manual MOTOROLA CONTENTS Paragraph Number Title Page Number ...

Страница 66: ...lxvi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA ...

Страница 88: ...1 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Страница 120: ...2 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Страница 138: ...Part II iv MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II Configuration and Reset ...

Страница 184: ...4 46 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II ConÞguration and Reset ...

Страница 202: ...Part III vi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Страница 266: ...8 34 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Страница 382: ...10 106 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Страница 392: ...11 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Страница 430: ...Part IV viii MOTOROLA Part IV Communications Processor Module ...

Страница 490: ...14 36 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 524: ...17 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 556: ...18 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 584: ...19 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 632: ...21 24 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 652: ...22 20 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 668: ...23 16 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 758: ...27 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 780: ...28 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 874: ...29 94 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 920: ...31 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 980: ...A 4 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Appendixes ...

Страница 1002: ...Index 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA INDEX ...

Страница 1006: ......