MOTOROLA

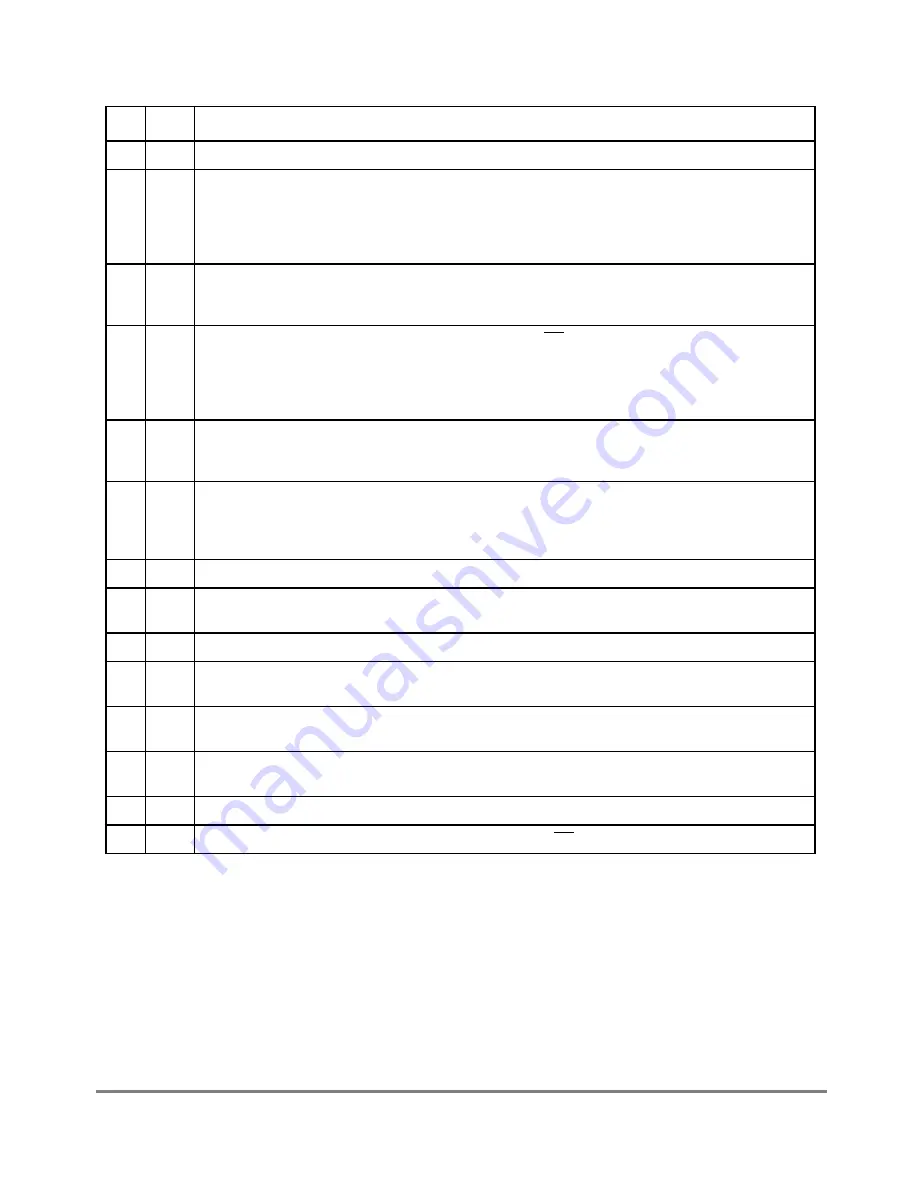

Chapter 22. SCC BISYNC Mode

22-13

Part IV. Communications Processor Module

Data length and buffer pointer Þelds are described in Section 19.2, ÒSCC Buffer

Descriptors (BDs).Ó Data length represents the number of octets the CP writes into this

buffer, including the BCS. For BISYNC mode, clear these bits. It is incremented each time

a received character is written to the buffer.

1

Ñ

Reserved, should be cleared.

2

W

Wrap (last BD in table).

0 Not the last BD in the table.

1 Last BD in the table. After this buffer is used, the CP receives incoming data into the Þrst BD that

RBASE points to. The number of BDs in this table is determined by the W bit and by overall space

constraints of the dual-port RAM.

3

I

Interrupt.

0 No interrupt is generated after this buffer is used.

1 SCCE[RXB] is set when the controller closes this buffer, which can cause an interrupt if it is enabled.

4

L

Last in frame. Set when this buffer is the last in a frame. If CD is negated in envelope mode or an error

is received, one or more of the OV, CD, and DE bits are set. The controller writes the number of frame

octets to the data length Þeld.

0 Not the Þrst buffer in the frame.

1 The Þrst buffer in the frame.

5

F

First in frame. Set when this is the Þrst buffer in a frame.

0 Not the Þrst buffer in a frame.

1 First buffer in a frame

6

CM

Continuous mode.

0 Normal operation.

1 The CP does not clear E after this BD is closed; the buffer is overwritten when the CP accesses this

BD next. However, E is cleared if an error occurs during reception, regardless of how CM is set.

7

Ñ

Reserved, should be cleared.

8

DE

DPLL error. Set when a DPLL error occurs during reception. In decoding modes where a transition is

should occur every bit, the DPLL error is set when a transition is missing.

9Ð10 Ñ

Reserved, should be cleared.

11

NO

Rx non-octet-aligned frame. Set when a frame is received containing a number of bits not evenly

divisible by eight.

12

PR

Parity error. Set when a character with parity error is received. Upon a parity error, the buffer is closed;

thus, the corrupted character is the last byte of the buffer. A new Rx buffer receives subsequent data.

13

CR

Rx CRC error. Set when this frame contains a CRC error. Received CRC bytes are always written to

the receive buffer.

14

OV

Overrun. Set when a receiver overrun occurs during frame reception.

15

CD

Carrier detect lost. Indicates when the carrier detect signal, CD, is negated during frame reception.

Table 22-11. SCC BISYNC RxBD Status and Control Field Descriptions (Continued)

Bits

Name

Description

Содержание MPC8260 PowerQUICC II

Страница 1: ...MPC8260UM D 4 1999 Rev 0 MPC8260 PowerQUICC II UserÕs Manual ª ª ...

Страница 32: ...xxxii MPC8260 PowerQUICC II UserÕs Manual MOTOROLA CONTENTS Paragraph Number Title Page Number ...

Страница 66: ...lxvi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA ...

Страница 88: ...1 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Страница 120: ...2 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Страница 138: ...Part II iv MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II Configuration and Reset ...

Страница 184: ...4 46 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II ConÞguration and Reset ...

Страница 202: ...Part III vi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Страница 266: ...8 34 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Страница 382: ...10 106 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Страница 392: ...11 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Страница 430: ...Part IV viii MOTOROLA Part IV Communications Processor Module ...

Страница 490: ...14 36 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 524: ...17 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 556: ...18 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 584: ...19 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 632: ...21 24 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 652: ...22 20 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 668: ...23 16 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 758: ...27 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 780: ...28 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 874: ...29 94 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 920: ...31 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 980: ...A 4 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Appendixes ...

Страница 1002: ...Index 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA INDEX ...

Страница 1006: ......