27-20

MPC8260 PowerQUICC II UserÕs Manual

MOTOROLA

Part IV. Communications Processor Module

Table 27-14 describes interrupt circular table Þelds.

Bits

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

Field

V

W

Ñ

UN

TXB

Ñ

NID

IDL

MRF RXF

BSY

RXB

R/W

R/W

Bits

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

Field

Ñ

Channel Number

0

0

0

0

0

0

R/W

R/W

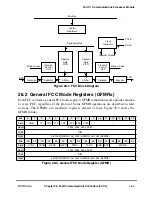

Figure 27-14. Interrupt Circular Table Entry

Table 27-14. Interrupt Circular Table Entry Field Descriptions

Bits

Name

Description

0

V

Valid bit. V = 1 indicates that this entry contains valid interrupt information. Upon generating a new

entry, the CP sets V = 1. The user clears V immediately after it reads the interrupt ßags of the entry

(before processing the interrupt). The V bits in the table are user-initialized. During initialization, the

user must clear those bits in all table entries.

1

W

Wrap bit. W = 1 indicates the last interrupt circular table entry. The next eventÕs entry is written/read

(by CP/user) from the address contained in INTBASE (see Table 27-1). During initialization, the user

must clear all W bits in the table except for the last one which must be set.

2Ð5

Ñ

Reserved, should be cleared.

6

UN

Tx no data. The CP sets this ßag if there is no data available to be sent to the transmitter. The

transmitter sends an ABORT indication and then sends idles.

7

TXB

Tx buffer. A buffer has been completely transmitted. TXB is set (and an interrupt request is

generated) as soon as the programmed number of PAD characters (or the closing ßag, for PAD = 0)

is written to MCC transmit FIFO. This controls when the TXB interrupt is given in relation to the

closing ßag sent out at TXD. Section 27.11.2, ÒTransmit Buffer Descriptor (TxBD)Ó describes how

PAD characters are used.

8Ð9

Ñ

Reserved, should be cleared.

10

MRF

Maximum receive frame length violation. This interrupt occurs in HDLC mode when more bytes are

received than the value speciÞed in MFLR. This interrupt is generated as soon as the MFLR value is

exceeded; the remainder of the frame is discarded

11

NID

Set whenever a pattern that is not an idle pattern is identiÞed.

12

IDL

Idle. Set when the channelÕs receiver identiÞes the Þrst occurrence of HDLC idle (0xFFFE) after any

non-idle pattern.

13

RXF

Rx frame. A complete HDLC frame has been received.

14

BSY

Busy. A frame was received but was discarded due to lack of buffers.

15

RXB

Rx buffer. A buffer has been received on this channel that was not the last buffer in frame. This

interrupt is also given for different error types that can happen during reception. Error conditions are

reported in the RxBD.

16Ð18 Ñ

Reserved, should be cleared.

19Ð26 CN

Channel number. IdentiÞes the requests channel index (0Ð255).

27Ð31 Ñ

Reserved, should be cleared.

Содержание MPC8260 PowerQUICC II

Страница 1: ...MPC8260UM D 4 1999 Rev 0 MPC8260 PowerQUICC II UserÕs Manual ª ª ...

Страница 32: ...xxxii MPC8260 PowerQUICC II UserÕs Manual MOTOROLA CONTENTS Paragraph Number Title Page Number ...

Страница 66: ...lxvi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA ...

Страница 88: ...1 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Страница 120: ...2 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Страница 138: ...Part II iv MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II Configuration and Reset ...

Страница 184: ...4 46 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II ConÞguration and Reset ...

Страница 202: ...Part III vi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Страница 266: ...8 34 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Страница 382: ...10 106 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Страница 392: ...11 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Страница 430: ...Part IV viii MOTOROLA Part IV Communications Processor Module ...

Страница 490: ...14 36 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 524: ...17 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 556: ...18 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 584: ...19 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 632: ...21 24 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 652: ...22 20 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 668: ...23 16 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 758: ...27 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 780: ...28 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 874: ...29 94 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 920: ...31 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 980: ...A 4 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Appendixes ...

Страница 1002: ...Index 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA INDEX ...

Страница 1006: ......