MOTOROLA

Chapter 20. SCC UART Mode

20-17

Part IV. Communications Processor Module

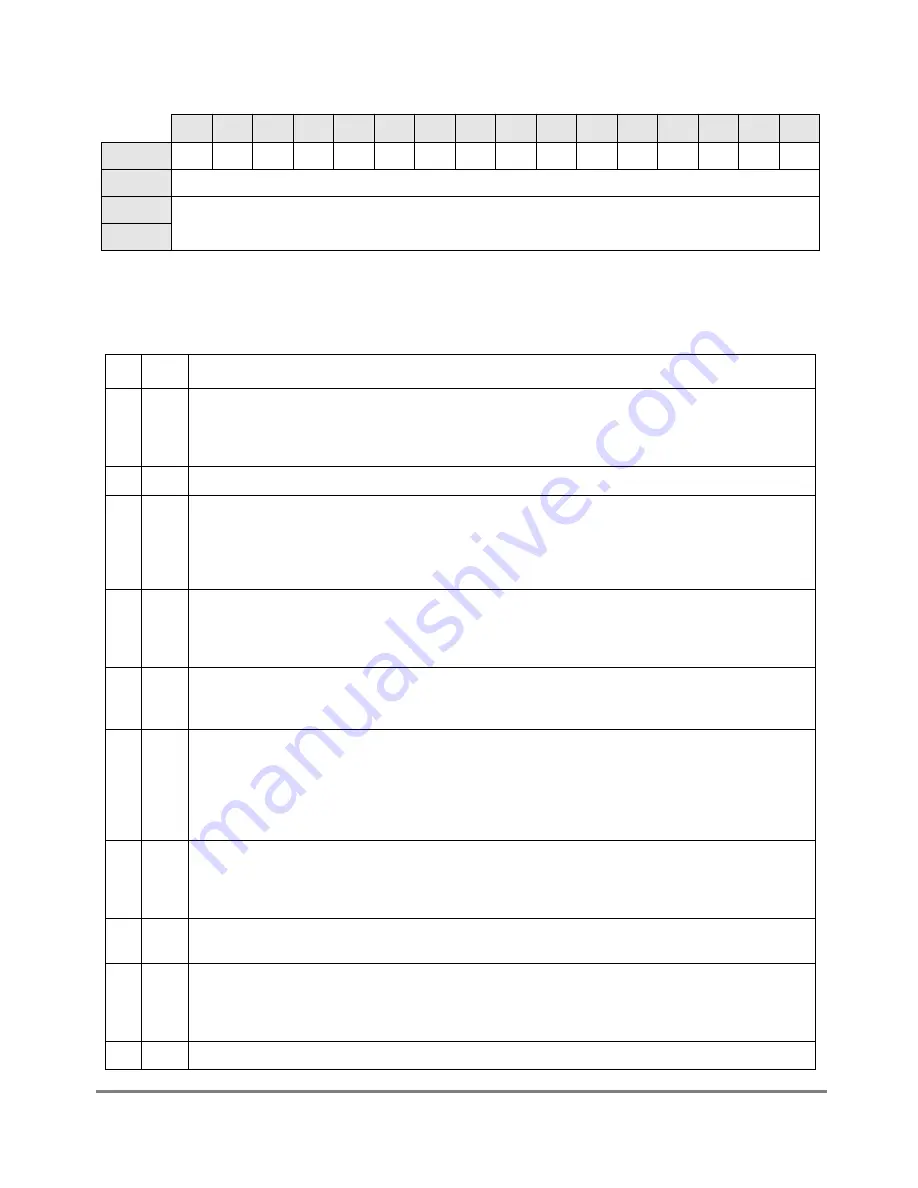

Figure 20-8 shows the SCC UART RxBD.

Table 20-10 describes RxBD status and control Þelds.

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

0

E

Ñ

W

I

C

A

CM

ID

AM

Ñ

BR

FR

PR

Ñ

OV

CD

2

Data Length

4

Rx Buffer Pointer

6

Figure 20-8. SCC UART Receive Buffer Descriptor (RxBD)

Table 20-10. SCC UART RxBD Status and Control Field Descriptions

Bits Name

Description

0

E

Empty.

0 The buffer is full or reception was aborted due to an error. The core can read or write to any Þelds of

this BD. The CPM does not reuse this BD while E = 0.

1 The buffer is not full. The CPM controls this BD and buffer. The core should not modify this BD.

1

Ñ

Reserved, should be cleared.

2

W

Wrap (last buffer descriptor in the BD table).

0 Not the last descriptor in the table.

1 Last descriptor in the table. After this buffer is used, the CPM receives incoming data using the BD

pointed to by RBASE. The number of BDs in this table is programable and determined only by the W

bit and overall space constraints of the dual-port RAM.

3

I

Interrupt.

0 No interrupt is generated after this buffer is Þlled.

1 The CP sets SCCE[RX] when this buffer is completely Þlled by the CPM, indicating the need for the

core to process the buffer. Setting SCCE[RX] causes an interrupt if not masked.

4

C

Control character.

0 This buffer does not contain a control character.

1 The last byte in this buffer matches a user-deÞned control character.

5

A

Address.

0 The buffer contains only data.

1 For manual multidrop mode, A indicates the Þrst byte of this buffer is an address byte. Software should

perform address comparison. In automatic multidrop mode, A indicates the buffer contains a message

received immediately after an address matched UADDR1 or UADDR2. The address itself is not written

to the buffer but is indicated by the AM bit.

6

CM

Continuous mode.

0 Normal operation. The CPM clears E after this BD is closed.

1 The CPM does not clear E after this BD is closed, allowing the buffer to be overwritten when the CPM

accesses this BD again. E is cleared if an error occurs during reception, regardless of CM.

7

ID

Buffer closed on reception of idles. The buffer is closed because a programmable number of consecutive

idle sequences (MAX_IDL) was received.

8

AM

Address match. SigniÞcant only if the address bit is set and automatic multidrop mode is selected in

PSMR[UM]. After an address match, AM identiÞes which user-deÞned address character was matched.

0 The address matched the value in UADDR2.

1 The address matched the value in UADDR1.

9

Ñ

Reserved, should be cleared.

Содержание MPC8260 PowerQUICC II

Страница 1: ...MPC8260UM D 4 1999 Rev 0 MPC8260 PowerQUICC II UserÕs Manual ª ª ...

Страница 32: ...xxxii MPC8260 PowerQUICC II UserÕs Manual MOTOROLA CONTENTS Paragraph Number Title Page Number ...

Страница 66: ...lxvi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA ...

Страница 88: ...1 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Страница 120: ...2 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Страница 138: ...Part II iv MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II Configuration and Reset ...

Страница 184: ...4 46 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II ConÞguration and Reset ...

Страница 202: ...Part III vi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Страница 266: ...8 34 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Страница 382: ...10 106 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Страница 392: ...11 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Страница 430: ...Part IV viii MOTOROLA Part IV Communications Processor Module ...

Страница 490: ...14 36 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 524: ...17 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 556: ...18 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 584: ...19 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 632: ...21 24 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 652: ...22 20 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 668: ...23 16 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 758: ...27 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 780: ...28 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 874: ...29 94 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 920: ...31 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Страница 980: ...A 4 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Appendixes ...

Страница 1002: ...Index 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA INDEX ...

Страница 1006: ......