•

Normal Pulse-Width Modulation (NPWM)

•

Dual-slope, interrupt/event at TOP (DSTOP)

•

Dual-slope, interrupt/event at ZERO (DSBOTTOM)

•

Dual-slope, interrupt/event at Top and ZERO (DSBOTH)

•

Dual-slope, critical interrupt/event at ZERO (DSCRITICAL)

When using MFRQ configuration, the TOP value is defined by the CC0 register value. For the other

waveform operations, the TOP value is defined by the Period (PER) register value.

For dual-slope waveform operations, the update time occurs when the counter reaches ZERO. For the

other waveforms generation modes, the update time occurs on counter wraparound, on overflow,

underflow, or re-trigger.

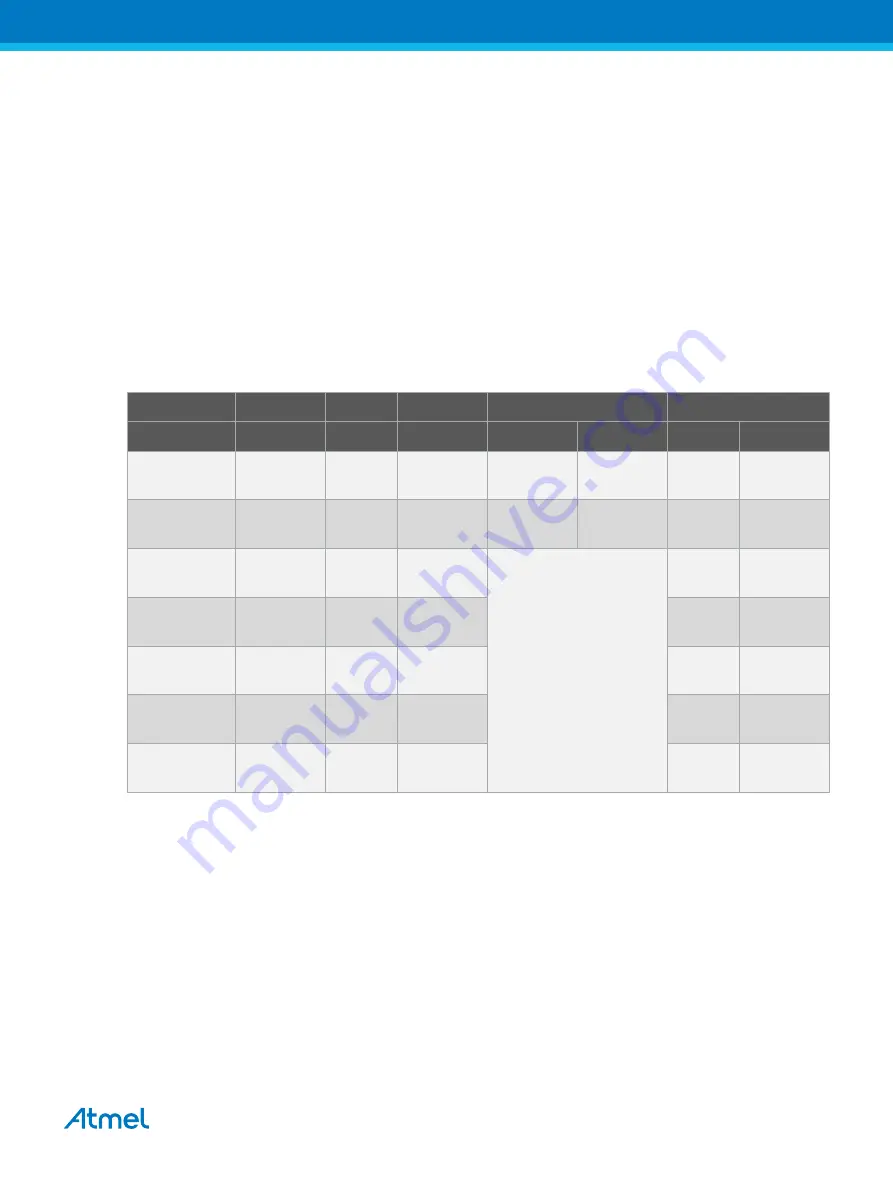

The table below shows the update counter and overflow event/interrupt generation conditions in different

operation modes.

Table 36-2. Counter Update and Overflow Event/interrupt Conditions

Name

Operation

TOP

Update

Output Waveform

OVFIF/Event

On Match

On Update Up

Down

NFRQ

Normal

Frequency

PER

TOP/

ZERO

Toggle

Stable

TOP

ZERO

MFRQ

Match

Frequency

CC0

TOP/

ZERO

Toggle

Stable

TOP

ZERO

NPWM

Single-

slope PWM

PER

TOP/

ZERO

See section 'Output

Polarity' below

TOP

ZERO

DSCRITICAL

Dual-slope

PWM

PER

ZERO

-

ZERO

DSBOTTOM

Dual-slope

PWM

PER

ZERO

-

ZERO

DSBOTH

Dual-slope

PWM

PER

TOP

ZERO

TOP

ZERO

DSTOP

Dual-slope

PWM

PER

ZERO

TOP

–

1.

The UPDATE condition on TOP only will occur when circular buffer is enabled for the channel.

Related Links

on page 812

on page 538

Normal Frequency (NFRQ)

For Normal Frequency generation, the period time (T) is controlled by the period register (PER). The

waveform generation output (WO[x]) is toggled on each compare match between COUNT and CCx, and

the corresponding Match or Capture Channel x Interrupt Flag (EVCTRL.MCEOx) will be set.

Atmel SAM L22G / L22J / L22N [DATASHEET]

Atmel-42402E-SAM L22G / L22J / L22N_Datasheet_Complete-07/2016

804