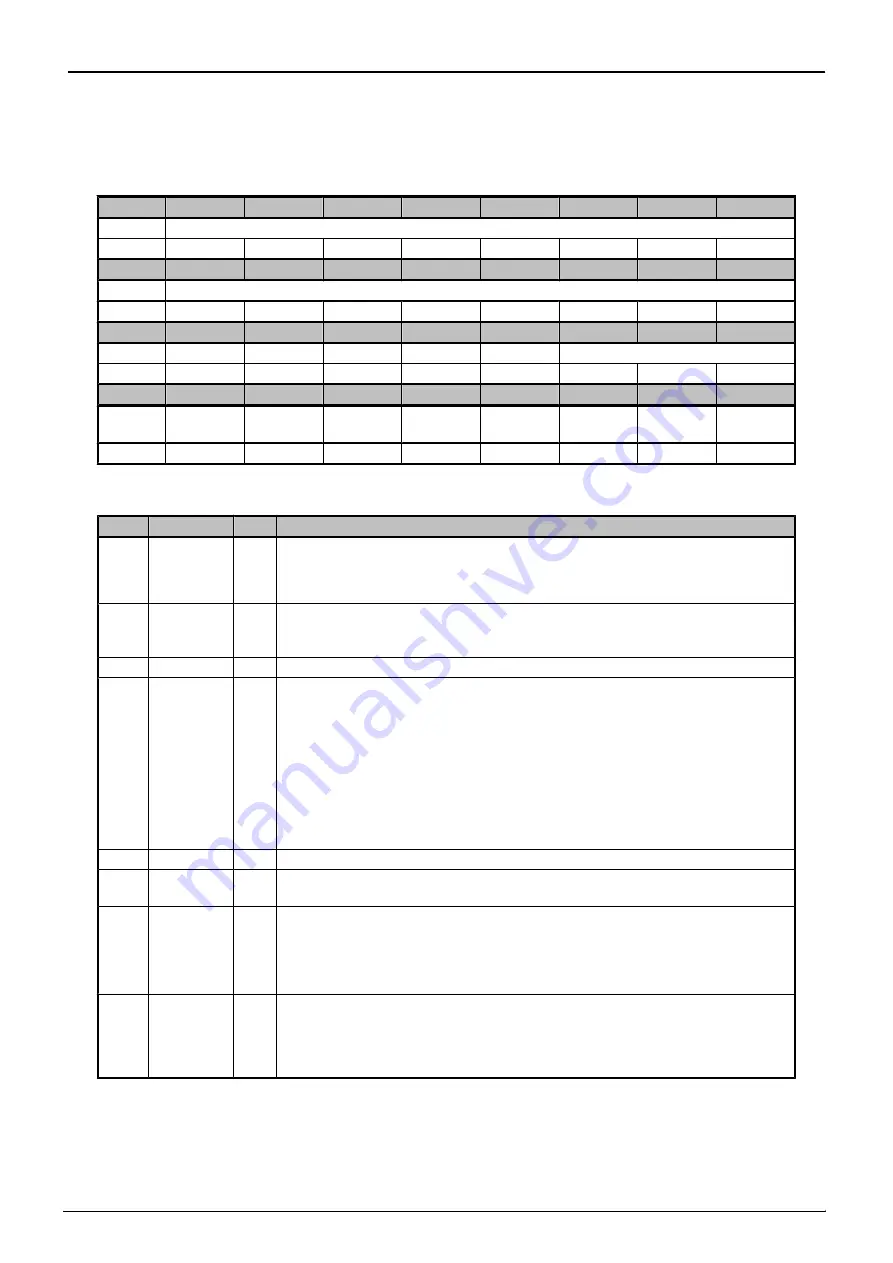

7.6.2.8 Application Interrupt and Reset Control Register

31

30

29

28

27

26

25

24

bit symbol

VECTKEY/VECTKEYSTAT

After reset

0

0

0

0

0

0

0

0

23

22

21

20

19

18

17

16

bit symbol

VECTKEY/VECTKEYSTAT

After reset

0

0

0

0

0

0

0

0

15

14

13

12

11

10

9

8

bit symbol

ENDIANESS

-

-

-

-

PRIGROUP

After reset

0

0

0

0

0

0

0

0

7

6

5

4

3

2

1

0

bit symbol

-

-

-

-

-

SYSRESET

REQ

VECTCLR

ACTIVE

VECTRESET

After reset

0

0

0

0

0

0

0

0

Bit

Bit Symbol

Type

Function

31-16

VECTKEY

(Write)/

VECTKEY-

STAT(Read)

R/W

Register key

[Write] Writing to this register requires 0x5FA in the <VECTKEY> field.

[Read] Read as 0xFA05.

15

ENDIANESS

R/W

Endianness bit:(Note1)

1: big endian

0: little endian

14-11

−

R

Read as 0.

10-8

PRIGROUP

R/W

Interrupt priority grouping

000: seven bits of pre-emption priority, one bit of subpriority

001: six bits of pre-emption priority, two bits of subpriority

010: five bits of pre-emption priority, three bits of subpriority

011: four bits of pre-emption priority, four bits of subpriority

100: three bits of pre-emption priority, five bits of subpriority

101: two bits of pre-emption priority, six bits of subpriority

110: one bit of pre-emption priority, seven bits of subpriority

111: no pre-emption priority, eight bits of subpriority

The bit configuration to split the interrupt priority register <PRI_n> into pre-emption priority and sub priority.

7-3

−

R

Read as 0.

2

SYSRESET

REQ

R/W

System Reset Request.

1=CPU outputs a SYSRESETREQ signal. (note2)

1

VECTCLR

ACTIVE

R/W

Clear active vector bit

1: clear all state information for active NMI, fault, and interrupts

0: do not clear.

This bit self-clears.

It is the responsibility of the application to reinitialize the stack.

0

VECTRESET

R/W

System Reset bit

1: reset system

0: do not reset system

Resets the system, with the exception of debug components (FPB, DWT and ITM) by setting "1" and this

bit is also zero cleared.

Note 1:

Little-endian is the default memory format for this product.

Note 2:

When

<

SYSRESETREQ

>

is output, warm reset is performed on this product. <SYSRESETREQ> is

cleared by warm reset.

TMPM3V6/M3V4

7. Exceptions

7.6 Exception/Interrupt-Related Registers

Page 114

2019-02-06

Summary of Contents for TMPM3V4

Page 1: ...32 Bit RISC Microcontroller TX03 Series TMPM3V6 M3V4 ...

Page 2: ... 2019 Toshiba Electronic Devices Storage Corporation ...

Page 7: ...Revision History Date Revision Comment 2019 02 06 1 First Release ...

Page 8: ......

Page 22: ...xiv ...

Page 52: ...TMPM3V6 M3V4 3 Processor Core 3 6 Exclusive access Page 30 2019 02 06 ...

Page 148: ...TMPM3V6 M3V4 7 Exceptions 7 6 Exception Interrupt Related Registers Page 126 2019 02 06 ...

Page 178: ...TMPM3V6 M3V4 9 Input Output port 9 2 Block Diagrams of Ports Page 156 2019 02 06 ...

Page 354: ...TMPM3V6 M3V4 14 Synchronous Serial Port SSP 14 6 Frame Format Page 332 2019 02 06 ...

Page 419: ...TMPM3V6 M3V4 Page 397 2019 02 06 ...

Page 462: ...TMPM3V6 M3V4 21 Watchdog Timer WDT 21 5 Control register Page 440 2019 02 06 ...

Page 544: ......