January 2007

149

Intel

®

855GME Chipset and Intel

®

6300ESB ICH Embedded Platform Design Guide

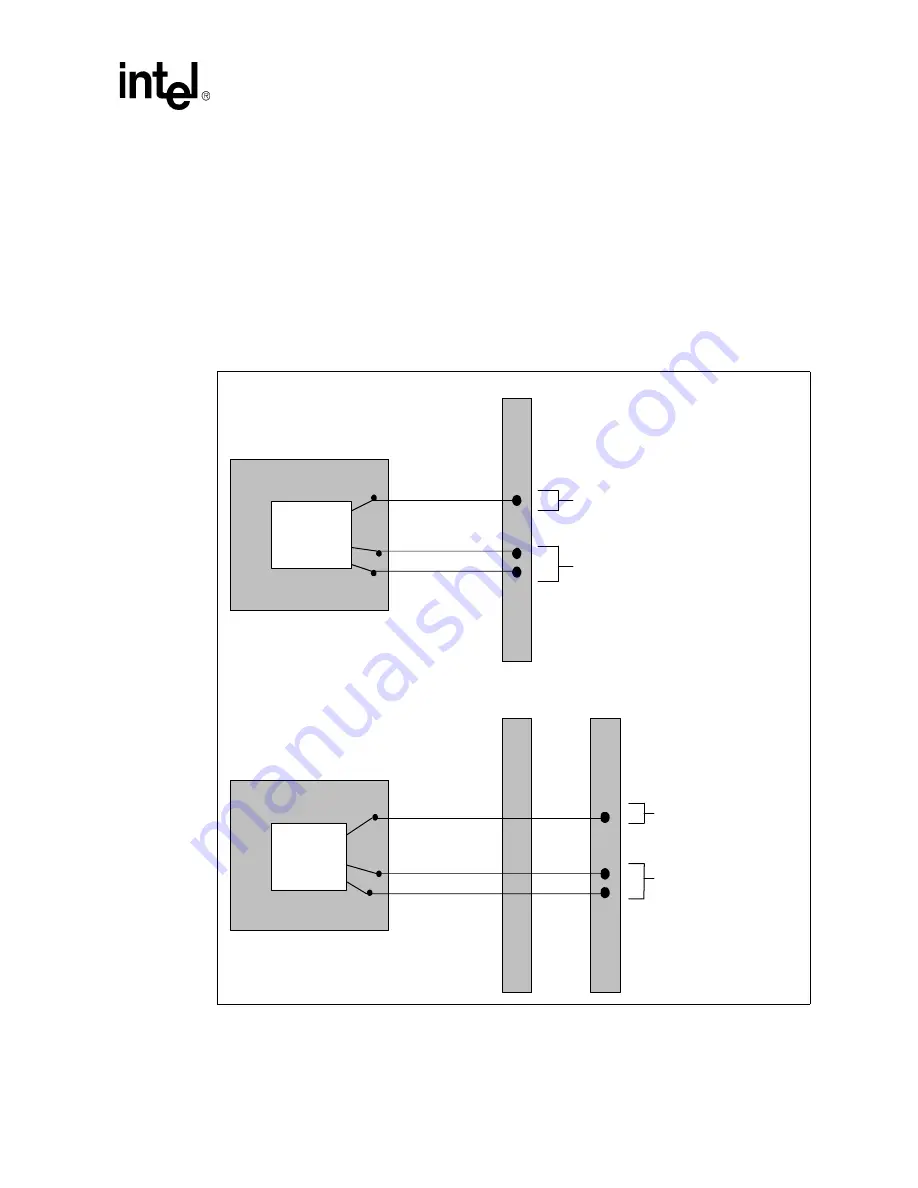

System Memory Design Guidelines (DDR-SDRAM)

Length range formula for DIMM1:

X

1

= SCK[5:3]/SCK[5:3]# total reference length, including package length. Refer to

for more information.

Y

1

= SMAB[5,4,2,1] total length = GMCH Package L1, as shown in

, where:

(X

1

– 1.5”)

≤

Y

1

≤

(X

1

- 0.5”)

No length matching is required from DIMM1 to the termination resistor.

depicts the

length matching requirements between the CPC signals and clock. A nominal CPC package length

of 500 mils may be used to estimate baseline Mbyte lengths.

Figure 74. CPC Signals to Clock Length Matching Diagram

DIMM0

GMCH Package

SMA[5,4,2,1]

SCK[2:0]

SCK#[2:0]

Note: All lengths are measured from GMCH

die pad to DIMM connector pad.

CPC Length = Y0

Clock Reference Length = X0

DIMM0

DIMM1

SCK[5:3]

SCK#[5:3]

Clock Ref Length = X1

Note: All lengths are measured from GMCH

die pad to DIMM connector pad.

SMAB[5,4,2,1]

CPC Length = Y1

(X0 – 1.5") <= Y0 <= (X0 - 0.5")

(X1–1.5") <= Y1 <= (X1-0.5")

GMCH Package

855GME

GMCH

Die

855GME

GMCH

Die

Summary of Contents for 6300ESB ICH

Page 24: ...24 Intel 855GME Chipset and Intel 6300ESB ICH Embedded Platform Design Guide Introduction...

Page 102: ...102 Intel 855GME Chipset and Intel 6300ESB ICH Embedded Platform Design Guide...

Page 122: ...122 Intel 855GME Chipset and Intel 6300ESB ICH Embedded Platform Design Guide...

Page 190: ...190 Intel 855GME Chipset and Intel 6300ESB ICH Embedded Platform Design Guide Hub Interface...

Page 318: ...318 Intel 855GME Chipset and Intel 6300ESB ICH Embedded Platform Design Guide Layout Checklist...