MC96F6432

June 22, 2018 Ver. 2.9

169

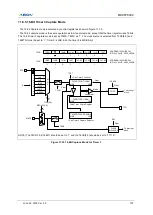

P

r

e

s

c

a

l

e

r

fx

M

U

X

fx/2

T4CNT/T3CNT (16Bit)

EC3

fx/4

fx/8

fx/32

fx/128

fx/512

fx/2048

3

T3CK[2:0]

T3CN

16-bit Timer 3 Counter

T4DR/T3DR (16Bit)

Comparator

T3IFR

To interrupt

block

T3O

16-bit Timer 3 Data Register

INT_ACK

Clear

Clear

Match

T4CAPR/T3CAPR (16Bit)

Clear

EINT0

EIPOL0L[1:0]

FLAG0

(EIFLAG0.0)

INT_ACK

Clear

To interrupt

block

2

T3MS

T3ST

16-bit Timer 3 Capture Register

MSB LSB

MSB LSB

MSB LSB

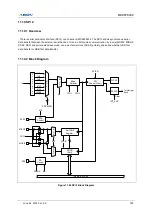

NOTE) The T4CR.7 bit (16BIT) should be set to

‘1’ and the T4CK[3:0] should be set to “1111b”.

Figure 11.46 16-Bit Timer 3 Block Diagram

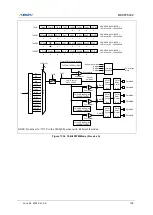

P

r

e

s

c

a

l

e

r

fx

M

U

X

fx/2

fx/4

fx/16

fx/32

fx/64

fx/8

fx/1

Comparator

10-bit Counter

2Bit + T4CNT

10-bit A Data Register

T4ADRH/T4ADRL

Control

Up/Down

Comparator

T4PPRH/T4PPRL (10Bit)

Period Match

PWM

Output

Control

A-ch

PWM4AA

T4CN

4

T4CK[3:0]

fx/128

fx/256

fx/1024

fx/2048

fx/4096

fx/512

fx/8192

fx/16384

Timer 4 PWM Period Register

T4ST

PWM

Delay

Control

A-ch

PWM4AB

Comparator

10-bit B Data Register

T4BDRH/T4BDRL

PWM

Output

Control

B-ch

PWM4BA

PWM

Delay

Control

B-ch

PWM4BB

Comparator

10-bit C Data Register

T4CDRH/T4CDRL

PWM

Output

Control

C-ch

PWM4CA

PWM

Delay

Control

C-ch

PWM4CB

A Match

B Match

C Match

Interrupt

Generator

A Match

B Match

C Match

Bottom (Underflow)

To interrupt

block

NOTE: Do not set to

“1111b” in the T4CK[3:0], when two 8-bit timer 3/4 modes.

Figure 11.47 10-Bit PWM Timer 4 Block Diagram

Summary of Contents for MC96F6432 Series

Page 24: ...MC96F6432 24 June 22 2018 Ver 2 9 4 Package Diagram Figure 4 1 48 Pin LQFP 0707 Package...

Page 25: ...MC96F6432 June 22 2018 Ver 2 9 25 Figure 4 2 44 Pin MQFP Package...

Page 26: ...MC96F6432 26 June 22 2018 Ver 2 9 Figure 4 3 32 Pin LQFP Package...

Page 27: ...MC96F6432 June 22 2018 Ver 2 9 27 Figure 4 4 32 Pin SOP Package...

Page 28: ...MC96F6432 28 June 22 2018 Ver 2 9 Figure 4 5 28 Pin SOP Package...