MC96F6432

June 22, 2018 Ver. 2.9

163

Figure 11.40 Example of Phase Correction and Frequency correction of PWM

External Sync

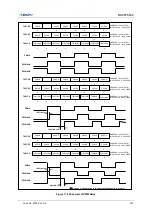

If using ESYNC bit of T4PCR1 register, it is possible to synchronize the output of PWM from external signal.

If ESYNC bit sets to ‘1’, the external signal moves to PWM module through the BLNK pin. If BLNK signal is low,

immediately PWM output becomes a reset value, and internal counter becomes reset. If BLNK signal returns to

‘1’, the counter is started again and PWM output is normally generated. (Figure 11.41 referred)

PWM Halt

If using PHLT bit of T4PCR1 register, it is possible to stop PWM operation by the software. During PHLT bit

being ‘1’, PWM output becomes a reset value, and internal counter becomes reset as 0. Without changing PWM

setting, temporarily it is able to stop PWM. In case of T4CNT, when stopping counter, PWM output pin remains

before states. But if PHLT bit

sets to ‘1’, PWM output pin has reset value.

Figure 11.41 Example of PWM External Synchronization with BLNK Input

T4

00 01 02

12

T4PCR1 = 40

H

(EYNC=1)

T4PPRH = 00

H

T4PPRL = 2A

H

T4ADRH = 00

H

T4ADRL = 12

H

00

14

13

02

01

15

14

13

12

00

2A

29

03

02

01

14

13

12

00

2A

Source Clock

(f

x

)

01

BLNK

“1”

PWM OUTPUT

HIGH-Z

HZCLR

“1”

PWM Release

HIGH-Z

2A

02

P02/PWM

POLAA = 1

BLNK

ESYNC = 1

HIGH-Z

T4CNT

Duty1

Back-to-Back

mode

Output

00

H

00

H

00

H

MAX

MAX

MAX

Period1

Duty, Period Update

Duty2

Period2

Duty3

Period3

Overflow INT.

Overflow INT.

Bottom INT.

Overflow INT.

Interrupt Timing

Summary of Contents for MC96F6432 Series

Page 24: ...MC96F6432 24 June 22 2018 Ver 2 9 4 Package Diagram Figure 4 1 48 Pin LQFP 0707 Package...

Page 25: ...MC96F6432 June 22 2018 Ver 2 9 25 Figure 4 2 44 Pin MQFP Package...

Page 26: ...MC96F6432 26 June 22 2018 Ver 2 9 Figure 4 3 32 Pin LQFP Package...

Page 27: ...MC96F6432 June 22 2018 Ver 2 9 27 Figure 4 4 32 Pin SOP Package...

Page 28: ...MC96F6432 28 June 22 2018 Ver 2 9 Figure 4 5 28 Pin SOP Package...