MC96F6432

June 22, 2018 Ver. 2.9

133

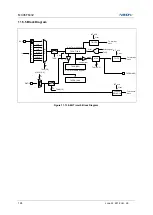

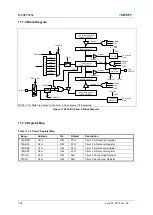

11.6.3 16-Bit Capture Mode

The 16-bit timer 1 capture mode is set by T1MS[1:0]

as ‘01’. The clock source can use the internal/external

clock. Basically, it has the same function as the 16-bit timer/counter mode and the interrupt occurs when

T1CNTH/T1CNTL is equal to T1ADRH/T1ADRL. The T1CNTH, T1CNTL values are automatically cleared by

match signal. It can be also cleared by software (T1CC).

This timer interrupt in capture mode is very useful when the pulse width of captured signal is wider than the

maximum period of timer.

The capture result is loaded into T1BDRH/T1BDRL.

According to EIPOL1 registers setting, the external interrupt EINT11 function is chosen. Of course, the EINT11

pin must be set as an input port.

A Match

T1CC

T1EN

P

r

e

s

c

a

l

e

r

fx

M

U

X

fx/2

fx/4

fx/64

fx/512

fx/2048

fx/8

fx/1

16-bit Counter

T1CNTH/T1CNTL

16-bit B Data Register

T1BDRH/T1BDRL

Clear

Edge

Detector

T1ECE

EC1

Comparator

16-bit A Data Register

T1ADRH/T1ADRL

T1IFR

INT_ACK

Clear

To interrupt

block

A Match

Buffer Register A

A Match

T1CC

Reload

R

EINT11

T1CNTR

T1EN

3

T1CK[2:0]

Clear

EIPOLB[1:0]

FLAG11

(EIFLAG1.2)

INT_ACK

Clear

To interrupt

block

2

T1MS[1:0]

2

T1EN

T1CRH

1

ADDRESS:BBH

INITIAL VALUE : 0000_0000B

–

T1MS1

T1MS0

–

–

–

T1CC

–

0

1

–

–

–

X

T1CK1

T1CRL

X

ADDRESS:BAH

INITIAL VALUE : 0000_0000B

T1CK1

T1CK0

T1IFR

–

T1POL

T1ECE T1CNTR

X

X

X

–

X

X

X

T1EN

Figure 11.16 16-Bit Capture Mode for Timer 1

Summary of Contents for MC96F6432 Series

Page 24: ...MC96F6432 24 June 22 2018 Ver 2 9 4 Package Diagram Figure 4 1 48 Pin LQFP 0707 Package...

Page 25: ...MC96F6432 June 22 2018 Ver 2 9 25 Figure 4 2 44 Pin MQFP Package...

Page 26: ...MC96F6432 26 June 22 2018 Ver 2 9 Figure 4 3 32 Pin LQFP Package...

Page 27: ...MC96F6432 June 22 2018 Ver 2 9 27 Figure 4 4 32 Pin SOP Package...

Page 28: ...MC96F6432 28 June 22 2018 Ver 2 9 Figure 4 5 28 Pin SOP Package...