MC96F6432

280

June 22, 2018 Ver. 2.9

LCDCRL (LCD Driver Control Low Register) : 99H

7

6

5

4

3

2

1

0

–

–

DBS3

DBS2

DBS1

DBS0

LCLK1

LCK0

–

–

R./W

R/W

R/W

R/W

R/W

R/W

Initial value : 00H

DBS[3:0]

LCD Duty and Bias Select (NOTE)

DBS3

DBS2

DBS1

DBS0 Description

0

0

0

0

1/8Duty, 1/4Bias (60k ohm)

0

0

0

1

1/6Duty, 1/4Bias (60k ohm)

0

0

1

0

1/5Duty, 1/3Bias (60k ohm)

0

0

1

1

1/4Duty, 1/3Bias (60k ohm)

0

1

0

0

1/3Duty, 1/3Bias (60k ohm)

0

1

0

1

1/3Duty, 1/2Bias (60k ohm)

0

1

1

0

1/3Duty, 1/2Bias (120k ohm)

0

1

1

1

1/2Duty, 1/2Bias (60k ohm)

1

0

0

0

1/2Duty, 1/2Bias (120k ohm)

Other values

Not available

LCLK[1:0]

LCD Clock Select (When f

WCK

(Watch timer clock)= 32.768 kHz)

LCLK1 LCLK0 Description

0

0

f

LCD

= 128Hz

0

1

f

LCD

= 256Hz

1

0

f

LCD

= 512Hz

1

1

f

LCD

= 1024Hz

NOTE) The LCD clock is generated by watch timer clock (f

WCK

). So

the watch timer should be enabled when the LCD display is turned on.

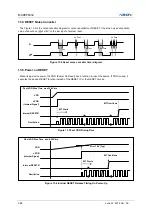

Table 11-27 LCD Frame Frequency

LCD Clock

Frequency (f

LCD

)

LCD Frame Frequency (f

FRAME

)

Unit

1/2 Duty

1/3 Duty

1/4 Duty

1/5 Duty

1/6 Duty

1/8 Duty

128

64

43

32

26

21

16

Hz

256

128

85

64

51

43

32

512

256

171

128

102

85

64

1024

512

341

256

205

171

128

The LCD frame frequency is calculated by the following formula:

LCD Frame Frequency (f

FRAME

) = f

LCD

× Duty[Hz]

Ex) In cace of 1/4 duty and f

LCD

= 512Hz, f

FRAME

= f

LCD

× 1/4 = 512 × 1/4 = 128[Hz]

Summary of Contents for MC96F6432 Series

Page 24: ...MC96F6432 24 June 22 2018 Ver 2 9 4 Package Diagram Figure 4 1 48 Pin LQFP 0707 Package...

Page 25: ...MC96F6432 June 22 2018 Ver 2 9 25 Figure 4 2 44 Pin MQFP Package...

Page 26: ...MC96F6432 26 June 22 2018 Ver 2 9 Figure 4 3 32 Pin LQFP Package...

Page 27: ...MC96F6432 June 22 2018 Ver 2 9 27 Figure 4 4 32 Pin SOP Package...

Page 28: ...MC96F6432 28 June 22 2018 Ver 2 9 Figure 4 5 28 Pin SOP Package...