MC96F6432

June 22, 2018 Ver. 2.9

179

T4PCR3 (Timer 4 PWM Control Register 3) : 1005H (ESFR)

7

6

5

4

3

2

1

0

HZCLR

POLBO

POLAA

POLAB

POLBA

POLBB

POLCA

POLCB

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Initial value : 00H

HZCLR

High-Impedance Output Clear Bit

0

No effect

1

Clear high-impedance output

(The PWM4xA/PWM4xB pins are back to output and this bit is

automatically cleared to logic

‘0’. where x = A, B and C)

POLBO

Configure PWM4AB/PWM4BB/PWMCB Channel Polarity When these

pins are disabled

0

These pins are output according to the polarity setting when

disable (POLAB/POLBB/POLCB bits)

1

These pins are same level as the PWM4xA pins regardless of

the polarity setting when disable (POLAB/POLBB/POLCB bits,

where x = A, B and C)

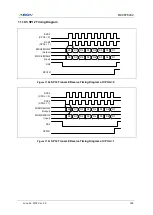

POLAA

Configure PWM4AA Channel Polarity

0

Start at high level (This pin is low level when disable)

1

Start at low level (This pin is high level when disable)

POLAB

Configure PWM4AB Channel Polarity

0

Non-inversion signal of PWM4AA pin

1

Inversion signal of PWM4AA pin

POLBA

Configure PWM4BA Channel Polarity

0

Start at high level (This pin is low level when disable)

1

Start at low level (This pin is high level when disable)

POLBB

Configure PWM4BB Channel Polarity

0

Non-inversion signal of PWM4BA pin

1

Inversion signal of PWM4BA pin

POLCA

Configure PWM4CA Channel Polarity

0

Start at high level (This pin is low level when disable)

1

Start at low level (This pin is high level when disable)

POLCB

Configure PWM4CB Channel Polarity

0

Non-inversion signal of PWM4CA pin

1

Inversion signal of PWM4CA pin

Summary of Contents for MC96F6432 Series

Page 24: ...MC96F6432 24 June 22 2018 Ver 2 9 4 Package Diagram Figure 4 1 48 Pin LQFP 0707 Package...

Page 25: ...MC96F6432 June 22 2018 Ver 2 9 25 Figure 4 2 44 Pin MQFP Package...

Page 26: ...MC96F6432 26 June 22 2018 Ver 2 9 Figure 4 3 32 Pin LQFP Package...

Page 27: ...MC96F6432 June 22 2018 Ver 2 9 27 Figure 4 4 32 Pin SOP Package...

Page 28: ...MC96F6432 28 June 22 2018 Ver 2 9 Figure 4 5 28 Pin SOP Package...