MC96F6432

June 22, 2018 Ver. 2.9

165

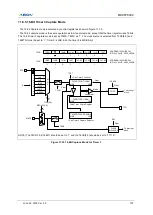

FORCE 6-Ch Drive

If FORCA

bit sets to ‘0’, it is possible to enable or disable PWM output pin and inversion output pin generated

through the duty counter of each channel. The inversion output is the reverse phase of the PWM output. A AA/AB

output of the A-channel duty register, a BA/BB output of the B-channel duty register, a CA/CB output of the C-

channel duty r

egister are controlled respectively. If the UALL bit is set to ‘1’, it is updated B/C channel duty at the

same time, when it is written by a A-channel duty register.

Figure 11.43 Example of Force Drive 6-ch Mode

PWMA

PAAOE

PWM4AA

PABOE

PWM4AB

PBAOE

PWM4BA

PBBOE

PWM4BB

FORCA

-

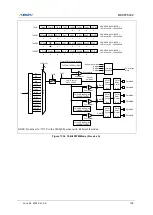

PAAOE PABOE PBAOE PBBOE PCAOE PCBOE

T4PCR2

0

-

X

X

X

X

X

X

ADDRESS : 1004H (ESFR)

INITIAL VALUE : 0-00_0000B

※

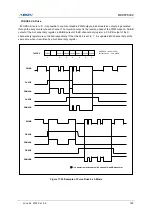

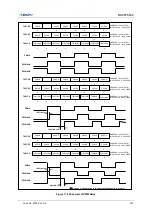

C-ch operation is the same with channel A and B waveform

PWMB

Summary of Contents for MC96F6432 Series

Page 24: ...MC96F6432 24 June 22 2018 Ver 2 9 4 Package Diagram Figure 4 1 48 Pin LQFP 0707 Package...

Page 25: ...MC96F6432 June 22 2018 Ver 2 9 25 Figure 4 2 44 Pin MQFP Package...

Page 26: ...MC96F6432 26 June 22 2018 Ver 2 9 Figure 4 3 32 Pin LQFP Package...

Page 27: ...MC96F6432 June 22 2018 Ver 2 9 27 Figure 4 4 32 Pin SOP Package...

Page 28: ...MC96F6432 28 June 22 2018 Ver 2 9 Figure 4 5 28 Pin SOP Package...