MC96F6432

136

June 22, 2018 Ver. 2.9

X

1

2

4

5

6

8

M-1

0

1

3

4

Timer 1 clock

Counter

T1ADRH/L

T1 Interrupt

PWM1O

B Match

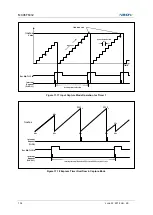

Repeat Mode(T1MS = 11b) and "Start High"(T1POL = 0b).

Set T1EN

0

Clear and Start

3

7

2

M

A Match

1. T1BDRH/L(5) < T1ADRH/L

PWM1O

A Match

2. T1BDRH/L >= T1ADRH/L

PWM1O

A Match

3. T1BDRH/L = "0000H"

Low Level

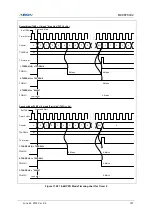

X

1

2

4

5

6

8

M-1

0

Timer 1 clock

Counter

T1ADRH/L

T1 Interrupt

PWM1O

B Match

One-shot Mode(T1MS = 10b) and "Start High"(T1POL = 0b).

Set T1EN

0

Clear and Start

3

7

M

A Match

1. T1BDRH/L(5) < T1ADRH/L

PWM1O

A Match

2. T1BDRH/L >= T1ADRH/L

PWM1O

A Match

3. T1BDRH/L = "0000H"

Low Level

Figure 11.20 16-Bit PPG Mode Timming chart for Timer 1

Summary of Contents for MC96F6432 Series

Page 24: ...MC96F6432 24 June 22 2018 Ver 2 9 4 Package Diagram Figure 4 1 48 Pin LQFP 0707 Package...

Page 25: ...MC96F6432 June 22 2018 Ver 2 9 25 Figure 4 2 44 Pin MQFP Package...

Page 26: ...MC96F6432 26 June 22 2018 Ver 2 9 Figure 4 3 32 Pin LQFP Package...

Page 27: ...MC96F6432 June 22 2018 Ver 2 9 27 Figure 4 4 32 Pin SOP Package...

Page 28: ...MC96F6432 28 June 22 2018 Ver 2 9 Figure 4 5 28 Pin SOP Package...