MC96F6432

104

June 22, 2018 Ver. 2.9

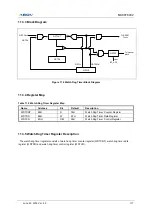

10.12.7 Register Description for Interrupt

IE (Interrupt Enable Register) : A8H

7

6

5

4

3

2

1

0

EA

–

INT5E

INT4E

INT3E

INT2E

INT1E

INT0E

R/W

–

R/W

R/W

R/W

R/W

R/W

R/W

Initial value : 00H

EA

Enable or Disable All Interrupt bits

0

All Interrupt disable

1

All Interrupt enable

INT5E

Enable or Disable External Interrupt 0 ~ 7 (EINT0 ~ EINT7)

0

Disable

1

Enable

INT4E

Enable or Disable USI1 Tx Interrupt

0

Disable

1

Enable

INT3E

Enable or Disable USI1 Rx Interrupt

0

Disable

1

Enable

INT2E

Enable or Disable USI1 I2C Interrupt

0

Disable

1

Enable

INT1E

Enable or Disable External Interrupt 11(EINT11)

0

Disable

1

Enable

INT0E

Enable or Disable External Interrupt 10 (EINT10)

0

Disable

1

Enable

Summary of Contents for MC96F6432 Series

Page 24: ...MC96F6432 24 June 22 2018 Ver 2 9 4 Package Diagram Figure 4 1 48 Pin LQFP 0707 Package...

Page 25: ...MC96F6432 June 22 2018 Ver 2 9 25 Figure 4 2 44 Pin MQFP Package...

Page 26: ...MC96F6432 26 June 22 2018 Ver 2 9 Figure 4 3 32 Pin LQFP Package...

Page 27: ...MC96F6432 June 22 2018 Ver 2 9 27 Figure 4 4 32 Pin SOP Package...

Page 28: ...MC96F6432 28 June 22 2018 Ver 2 9 Figure 4 5 28 Pin SOP Package...