MC96F6432

June 22, 2018 Ver. 2.9

207

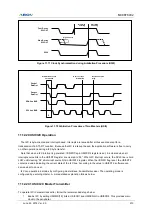

Figure 11.64 USI0 SPI Clock Formats when CPHA0=0

When CPHA0=0, the slave begins to drive its MISO0 output with the first data bit value when SS0 goes to active

low. The first SCK0 edge causes both the master and the slave to sample the data bit value on their MISO0 and

MOSI0 inputs, respectively. At the second SCK0 edge, the USI0 shifts the second data bit value out to the

MOSI0 and MISO0 outputs of the master and slave, respectively. Unlike the case of CPHA0=1, when CPHA0=0,

the slave’s SS0 input must go to its inactive high level between transfers. This is because the slave can prepare

the first data bit when it detects falling edge of SS0 input.

SCK0

(CPOL0=1)

MISO0

MOSI0

SCK0

(CPOL0=0)

/SS0 OUT

(MASTER)

BIT7

BIT0

/SS0 IN

(SLAVE)

BIT6

BIT1

…

…

BIT2

BIT5

BIT0

BIT7

BIT1

BIT6

SAMPLE

MSB First

LSB First

Summary of Contents for MC96F6432 Series

Page 24: ...MC96F6432 24 June 22 2018 Ver 2 9 4 Package Diagram Figure 4 1 48 Pin LQFP 0707 Package...

Page 25: ...MC96F6432 June 22 2018 Ver 2 9 25 Figure 4 2 44 Pin MQFP Package...

Page 26: ...MC96F6432 26 June 22 2018 Ver 2 9 Figure 4 3 32 Pin LQFP Package...

Page 27: ...MC96F6432 June 22 2018 Ver 2 9 27 Figure 4 4 32 Pin SOP Package...

Page 28: ...MC96F6432 28 June 22 2018 Ver 2 9 Figure 4 5 28 Pin SOP Package...