MC96F6432

June 22, 2018 Ver. 2.9

45

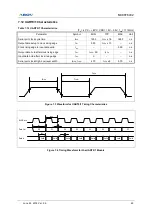

7.12 UART0/1 Characteristics

Table 7-12 UART0/1 Characteristics

(T

A

= -40°C ~ +85°C, VDD= 1.8V ~ 5.5V, f

XIN

=11.1MHz)

Parameter

Symbol

MIN

TYP

MAX

Unit

Serial port clock cycle time

t

SCK

1250

t

CPU

x 16

1650

ns

Output data setup to clock rising edge

t

S1

590

t

CPU

x 13

–

ns

Clock rising edge to input data valid

t

S2

–

–

590

ns

Output data hold after clock rising edge

t

H1

t

CPU

- 50

t

CPU

–

ns

Input data hold after clock rising edge

t

H2

0

–

–

ns

Serial port clock High, Low level width

t

HIGH

, t

LOW

470

t

CPU

x 8

970

ns

t

HIGH

t

LOW

t

SCK

Figure 7.3 Waveform for UART0/1 Timing Characteristics

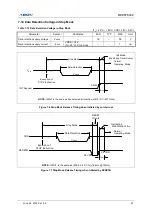

Shift Clock

Data Out

D1

D2

D3

D4

D5

D6

D7

D0

Valid

Data In

Valid

Valid

Valid

Valid

Valid

Valid

Valid

t

SCK

t

S1

t

H1

t

H2

t

S2

Figure 7.4 Timing Waveform for the UART0/1 Module

Summary of Contents for MC96F6432 Series

Page 24: ...MC96F6432 24 June 22 2018 Ver 2 9 4 Package Diagram Figure 4 1 48 Pin LQFP 0707 Package...

Page 25: ...MC96F6432 June 22 2018 Ver 2 9 25 Figure 4 2 44 Pin MQFP Package...

Page 26: ...MC96F6432 26 June 22 2018 Ver 2 9 Figure 4 3 32 Pin LQFP Package...

Page 27: ...MC96F6432 June 22 2018 Ver 2 9 27 Figure 4 4 32 Pin SOP Package...

Page 28: ...MC96F6432 28 June 22 2018 Ver 2 9 Figure 4 5 28 Pin SOP Package...