MC96F6432

June 22, 2018 Ver. 2.9

161

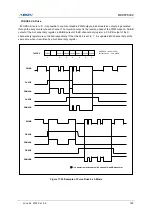

Figure 11.36 Example of PWM at 4 MHz

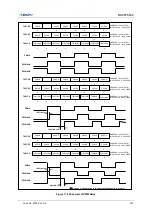

Figure 11.37 Example of Changing the Period in Absolute Duty Cycle at 4 MHz

Update period & duty register value at once

The period and duty of PWM comes to move from temporary registers to T4PPRH/L (PWM Period Register) and

T4ADRH/L/T4BDRH/L/T4CDRH/L (PWM Duty Register) when always period match occurs. If you want that the

period and duty is immediately changed, the UPDT bit in the T4PCR1

register must set to ‘1’. It should be noted

that it needs the 3 cycle of timer clock for data transfer in the internal clock synchronization circuit. So the update

data is written before 3 cycle of timer clock to get the right output waveform.

T4CNT

00 01 02 03 04

P02/PWM4AA

POLAA = 1

T4CR = 03

H

(2us)

T4PPRH = 00

H

T4PPRL = 0E

H

T4ADRH = 00

H

T4ADRL = 05

H

09

08

07

06

05

0D

0C

0B

0A

02

01

00

0E

06

05

04

03

0A

09

08

07

03

02

01

00

05

04

Source Clock

(f

x

)

06

Duty Cycle

(1+05

H

)X2us = 12us

Duty Cycle

(1+05

H

)X2us = 12us

Duty Cycle

(1+05

H

)X2us = 12us

Period Cycle

(1+0E

H

)X2us = 32us

31.25kHz

Period Cycle

(1+0A

H

)X2us = 22us

45.5kHz

Write 0A

H

to T4PPRL

Source Clock

(f

x

)

Duty Cycle(1+80

H

)X250ns = 32.25us

T4CNT

00

01

02

03

04

7F

80

81

82

3FF

00

01

02

P02/PWM4AA

POLAA = 1

P02/PWM4AA

POLAA = 0

Period Cycle(1+3FF

H

)X250ns = 256us

3.9kHz

T4PPRL(8 Bit)

T4ADRL(8 Bit)

T4PPRH(2 Bit)

T4ADRH(2 Bit)

03

H

FF

H

00

H

80

H

T4CR = 00

H

(f

XIN

)

T4PPRH = 03

H

T4PPRL = FF

H

T4ADRH = 00

H

T4ADRL = 80

H

Summary of Contents for MC96F6432 Series

Page 24: ...MC96F6432 24 June 22 2018 Ver 2 9 4 Package Diagram Figure 4 1 48 Pin LQFP 0707 Package...

Page 25: ...MC96F6432 June 22 2018 Ver 2 9 25 Figure 4 2 44 Pin MQFP Package...

Page 26: ...MC96F6432 26 June 22 2018 Ver 2 9 Figure 4 3 32 Pin LQFP Package...

Page 27: ...MC96F6432 June 22 2018 Ver 2 9 27 Figure 4 4 32 Pin SOP Package...

Page 28: ...MC96F6432 28 June 22 2018 Ver 2 9 Figure 4 5 28 Pin SOP Package...