MC96F6432

June 22, 2018 Ver. 2.9

151

T2CRL (Timer 2 Control Low Register) : CAH

7

6

5

4

3

2

1

0

T2CK2

T2CK1

T2CK0

T2IFR

–

T2POL

–

T2CNTR

R/W

R/W

R/W

R/W

–

R/W

–

R/W

Initial value : 00H

T2CK[2:0]

Select Timer 2 clock source. fx is main system clock frequency

T2CK2

T2CK1 T2CK0 Description

0

0

0

fx/512

0

0

1

fx/128

0

1

0

fx/32

0

1

1

fx/8

1

0

0

fx/4

1

0

1

fx/2

1

1

0

fx/1

1

1

1

T1 A Match

T2IFR

When T2 Match Interrupt occurs, this bit becomes

‘1’. For clearing bit,

write

‘0’ to this bit or auto clear by INT_ACK signal. Writing “1” has no

effect.

0

T2 interrupt no generation

1

T2 interrupt generation

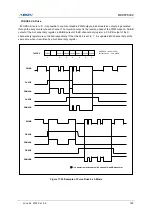

T2POL

T2O/PWM2O Polarity Selection

0

Start High (T2O/PWM2O is low level at disable)

1

Start Low (T2O/PWM2O is high level at disable)

T2CNTR

Timer 2 Counter Read Control

0

No effect

1

Load the counter value to the B data register (When write,

automatically cleared

“0” after being loaded)

Summary of Contents for MC96F6432 Series

Page 24: ...MC96F6432 24 June 22 2018 Ver 2 9 4 Package Diagram Figure 4 1 48 Pin LQFP 0707 Package...

Page 25: ...MC96F6432 June 22 2018 Ver 2 9 25 Figure 4 2 44 Pin MQFP Package...

Page 26: ...MC96F6432 26 June 22 2018 Ver 2 9 Figure 4 3 32 Pin LQFP Package...

Page 27: ...MC96F6432 June 22 2018 Ver 2 9 27 Figure 4 4 32 Pin SOP Package...

Page 28: ...MC96F6432 28 June 22 2018 Ver 2 9 Figure 4 5 28 Pin SOP Package...