MC96F6432

218

June 22, 2018 Ver. 2.9

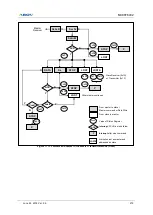

11.12.20.3 USI0 I2C Slave Transmitter

To operate I2C in slave transmitter, follow the recommended steps below.

1. If the main operating clock (SCLK) of the system is slower than that of SCL0, load value 0x00 into

USI0SDHR to make SDA0 change within one system clock period from the falling edge of SCL0. Note

that the hold time of SDA0 is calculated by SDAH x period of SCLK where SDAH is multiple of number

of SCLK coming from USI0SDHR. When the hold time of SDA0 is longer than the period of SCLK, I2C

(slave) cannot transmit serial data properly.

2. Enable I2C by setting USI0MS[1:0]

bits in USI0CR1 , IIC0IE bit in USI0CR4 and USI0EN bit in USI0CR2.

This provides main clock to the peripheral.

3. When a START condition is detected, I2C receives one byte of data and compares it with USI0SLA[6:0]

bits in USI0SAR. If the GCALL0 bit in USI0SAR is enabled, I2C compares the received data with value

0x00, the general call address.

4. If the received address does not equal to USI0SLA[6:0] bits in USI0SAR, I2C enters idle state ie, waits

for another START condition. Else if the address equals to USI0SLA[6:0] bits and the ACK0EN bit is

enabled, I2C generates SSEL0 interrupt and the SCL0 line is held LOW. Note that even if the address

equals to USI0SLA[6:0] bits, when the ACK0EN bit is disabled, I2C enters idle state. When SSEL0

interrupt occurs, load transmit data to USI0DR and clear to

“0b” all interrupt source bits in USI0ST2 to

release SCL0 line.

5. 1-Byte of data is being transmitted.

6. In this step, I2C generates TEND0 interrupt and holds the SCL0 line LOW regardless of the reception of

ACK signal from master. Slave can select one of the following cases.

1) No ACK signal is detected and I2C waits STOP or repeated START condition.

2) ACK signal from master is detected. Load data to transmit into USI0DR.

After doing one of the actions above, clear to

“0b” all interrupt source bits in USI0ST2 to release SCL0

line. In case of 1) move to step 7 to terminate communication. In case of 2) move to step 5. In either

case, a repeated START condition can be detected. For that case, move step 4.

7. This is the final step for slave transmitter function of I2C, handling STOP interrupt. The STOPC0 bit

indicates that data transfer between master and slave is over. To clear USI0ST2, write

“0” to USI0ST2.

After this, I2C enters idle state.

Summary of Contents for MC96F6432 Series

Page 24: ...MC96F6432 24 June 22 2018 Ver 2 9 4 Package Diagram Figure 4 1 48 Pin LQFP 0707 Package...

Page 25: ...MC96F6432 June 22 2018 Ver 2 9 25 Figure 4 2 44 Pin MQFP Package...

Page 26: ...MC96F6432 26 June 22 2018 Ver 2 9 Figure 4 3 32 Pin LQFP Package...

Page 27: ...MC96F6432 June 22 2018 Ver 2 9 27 Figure 4 4 32 Pin SOP Package...

Page 28: ...MC96F6432 28 June 22 2018 Ver 2 9 Figure 4 5 28 Pin SOP Package...