IDT Configuration Registers

PES12T3G2 User Manual

8 - 29

January 28, 2013

Notes

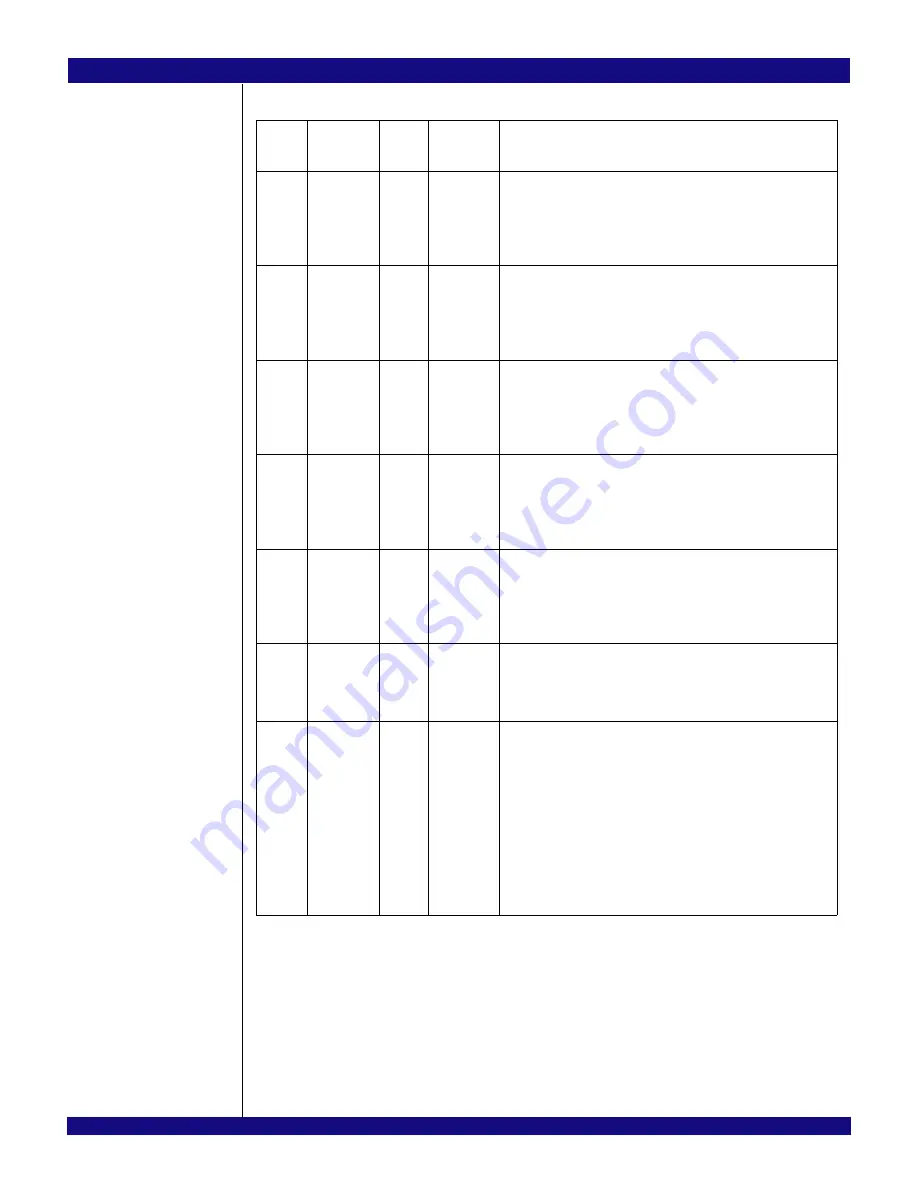

PCIESCTL - PCI Express Slot Control (0x058)

Bit

Field

Field

Name

Type Default

Value

Description

0

ABPE

RW

0x0

Attention Button Pressed Enable. This bit when set enables

generation of a Hot-Plug interrupt or wake-up event on an attention

button pressed event.

This bit is read-only and has a value of zero when the correspond-

ing capability is not enabled in the PCIESCAP register.

1

PFDE

RW

0x0

Power Fault Detected Enable. This bit when set enables the gen-

eration of a Hot-Plug interrupt or wake-up event on a power fault

event.

This bit is read-only and has a value of zero when the correspond-

ing capability is not enabled in the PCIESCAP register.

2

MRLSCE

RW

0x0

MRL Sensor Change Enable. This bit when set enables the gen-

eration of a Hot-Plug interrupt or wake-up event on a MRL sensor

change event.

This bit is read-only and has a value of zero when the correspond-

ing capability is not enabled in the PCIESCAP register.

3

PDCE

RW

0x0

Presence Detected Changed Enable. This bit when set enables

the generation of a Hot-Plug interrupt or wake-up event on a pres-

ence detect change event.

This bit is read-only and has a value of zero when the correspond-

ing capability is not enabled in the PCIESCAP register.

4

CCIE

RW

0x0

Command Complete Interrupt Enable. This bit when set enables

the generation of a Hot-Plug interrupt when a command is com-

pleted by the Hot-Plug Controller.

This bit is read-only and has a value of zero when the correspond-

ing capability is not enabled in the PCIESCAP register.

5

HPIE

RW

0x0

Hot Plug Interrupt Enable. This bit when set enables generation

of a Hot-Plug interrupt on enabled Hot-Plug events.

This bit is read-only and has a value of zero when the correspond-

ing capability is not enabled in the PCIESCAP register.

7:6

AIC

RW

0x3

Attention Indicator Control. When read, this register returns the

current state of the Attention Indicator. Writing to this register sets

the indicator.

This bit is read-only and has a value of zero when the correspond-

ing capability is not enabled in the PCIESCAP register.

This field is always zero if the ATTIP bit is cleared in the PCIES-

CAP register.

0x0 - (reserved) Reserved

0x1 - (on) On

0x2 - (blink) Blink

0x3 - (off) Off

Summary of Contents for 89HPES12T3G2

Page 10: ...IDT Table of Contents PES12T3G2 User Manual iv January 28 2013 Notes...

Page 12: ...IDT List of Tables PES12T3G2 User Manual vi January 28 2013 Notes...

Page 14: ...IDT List of Figures PES12T3G2 User Manual viii January 28 2013 Notes...

Page 18: ...IDT Register List PES12T3G2 User Manual xii January 28 2013 Notes...

Page 46: ...IDT Link Operation PES12T3G2 User Manual 3 10 January 28 2013 Notes...

Page 66: ...IDT SMBus Interfaces PES12T3G2 User Manual 5 18 January 28 2013 Notes...

Page 70: ...IDT Power Management PES12T3G2 User Manual 6 4 January 28 2013 Notes...

Page 138: ...IDT Configuration Registers PES12T3G2 User Manual 8 62 January 28 2013 Notes...