169

and maintain it; when detection value arriving at reset value 8, the relay output valid signal of one cycle impulse and the

counter is cleared, meanwhile, Y1 and relay will revoke output signal.

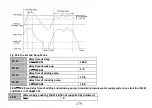

Fig. F7-9 Counter Reset and Detection Setting

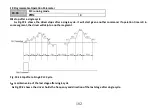

F7.34

Time out processing

0

~

3

3

0

:

stop timing, stop output

1

:

stop timing, continue output

2

:

cycle timing, stop output

3

:

cycle timing, continue output

This action is executed when the counting value arrives at preset value of F7.36.

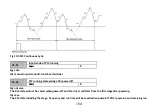

F7.35

Timing start condition

0

~

1

1

0

:

start during power on

1

:

start in running status, stop in stop status.

F7.36

Timing setting

0

~

65535s

0